Figure48 hi programming model–dsp viewpoint, 1 hi control register (hcr), Hi control register (hcr) -14 – Motorola DSP56012 User Manual

Page 94: Figure 4-8, Hi programming model–dsp viewpoint -14, There are

4-14

DSP56012 User’s Manual

MOTOROLA

Parallel Host Interface

Host Interface (HI)

The following paragraphs describe the purpose and operation of each bit in each

register of the HI that is visible to the DSP. The effects of the different types of reset

on these registers are shown. A brief discussion of interrupts and operation of the

DSP side of the HI complete the programming model from the DSP viewpoint. The

programming model from the host viewpoint begins at

Section

Programming Model—Host Processor Viewpoint

4.4.4.1

HI Control Register (HCR)

The HI Control Register (HCR) is an 8-bit read/write control register used by the

DSP to control the host interrupts and flags. The HCR cannot be accessed by the host

processor. It occupies the low-order byte of the internal data bus; the high-order

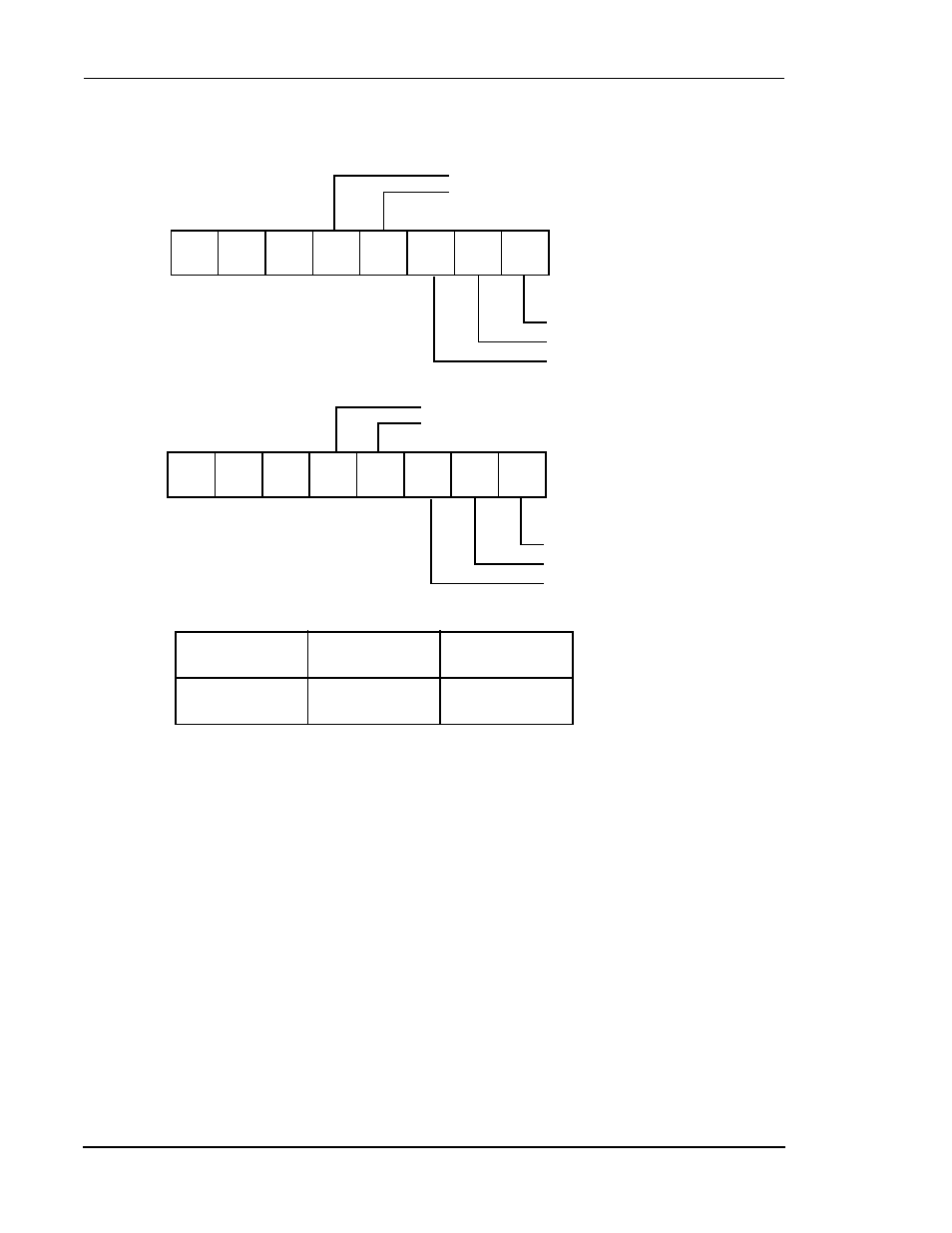

Figure 4-8 HI Programming Model–DSP Viewpoint

X:$FFE8

DSP CPU Flags

Host Flag 3

Host Flag 2

Interrupt Enables

Host Receive

Host Transmit

Host Command

Host Control Register (HCR)

(Read/Write)

X:$FFE9

Host Flags

Host Flag 1

Host Flag 0

Host Receive Data Full

Host Transmit Data Empty

Host Command Pending

Host Status Register (HSR)

(Read Only)

X:$FFEB

X:$FFEB

Receive

High Byte

Receive

Middle Byte

Receive

Low Byte

Transmit

High Byte

Transmit

Middle Byte

Transmit

Low Byte

Note:

1.

The numbers in parentheses are reset initialization values.

0

0

0

HF3

(0)

HF2

(0)

HCIE

(0)

HTIE

(0)

HRIE

(0)

7

0

DMA

(0)

0

0

HF1

(0)

HF0

(0)

HCP

(0)

HTDE

(1)

HRDF

(0)

7

0

Host Receive Data

Register (HORX) (Read Only)

Host Transmit Data

Register (HOTX) (Write Only

)

23

16 15

8

7

0

7

0 7

0

7

0

AA0315k