Figure82 dax programming mode, 1 dax audio data registers a and b (xadra/xadrb), 2 dax audio data buffer (xadbuf) – Motorola DSP56012 User Manual

Page 217: Dax audio data registers a and b (xadra/xadrb) -7, Dax audio data buffer (xadbuf) -7, Figure 8-2, Dax programming mode -7

Digital Audio Transmitter

DAX Internal Architecture

MOTOROLA

DSP56012 User’s Manual

8-7

8.5.1

DAX Audio Data Registers A and B (XADRA/XADRB)

XADRA and XADRB are 24-bit write-only registers. One frame of audio data, which

is to be transmitted in the next frame slot, is stored in these registers. The XADRA

and the XADRB are mapped to the same X Memory I/O address. Successive write

accesses to this address will access XADRA and XADRB alternately. When a new

frame transmission starts, write access to the XADRA is enabled to ensure that

accessing the XADRA always occurs first within an interrupt service. When the

XADRB is accessed, the XADE bit in the XSTR is cleared.

8.5.2

DAX Audio Data Buffer (XADBUF)

XADBUF is a 24-bit register that holds Channel B audio data for the current frame

while Channel A audio and non-audio data are being transmitted. At the beginning

of a frame transmission, audio data stored in the XADRA is directly transferred to

the XADSR for Channel A transmission, and at the same time the Channel B audio

data stored in XADRB is transferred to the XADBUF. The Channel B audio data in

the XADBUF is transferred to the XADSR at the beginning of the Channel B

transmission. This double buffering mechanism provides more cycles to write the

next audio data to XADRA and XADRB. This register is not directly accessible by

DSP instructions.

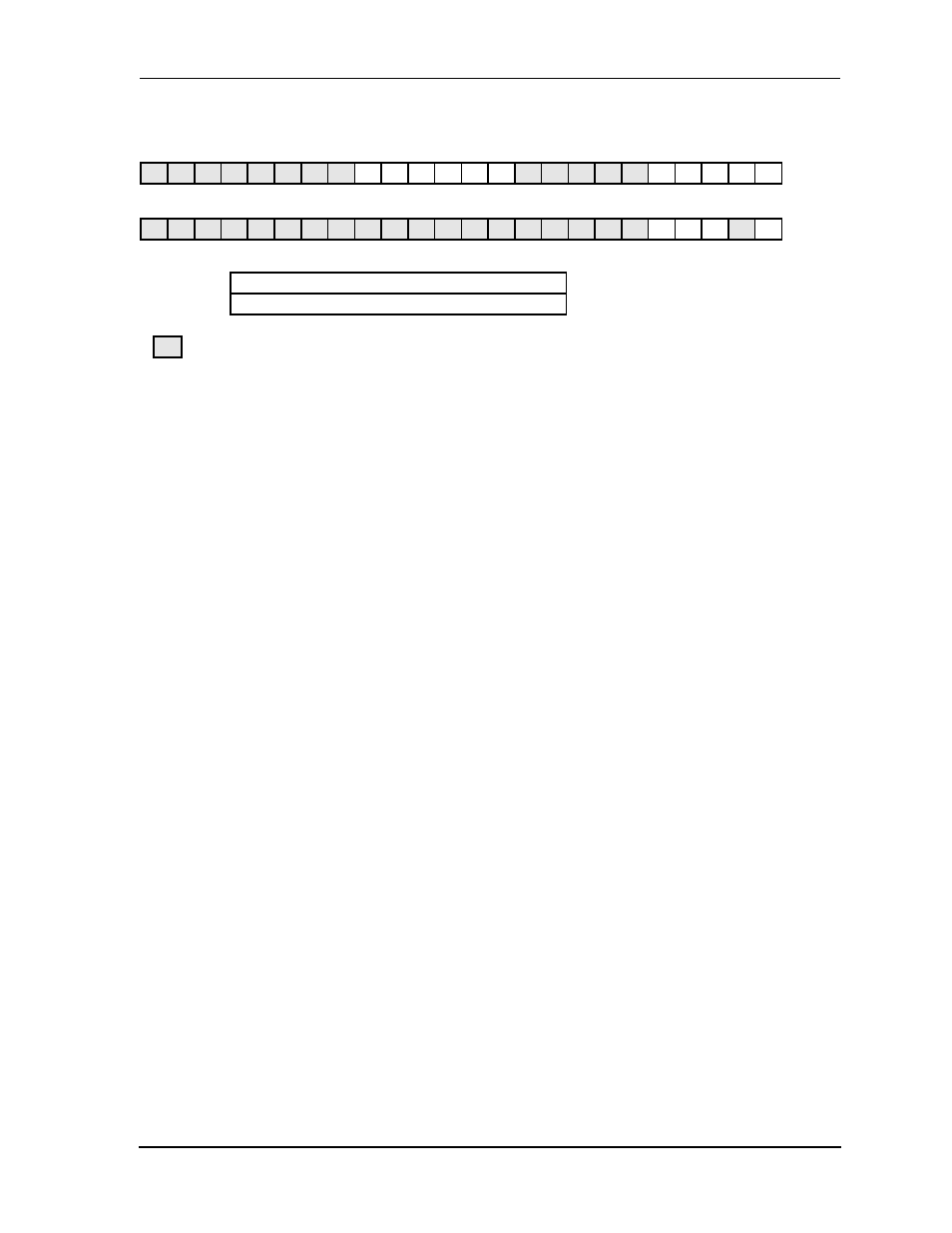

Figure 8-2 DAX Programming Mode

XCTR

XADRA

XADRB

X:$FFDC

Accessed Alternately

23

0

X:$FFDE

0

23

XSTP XIEN XEN

1

2

21

22

8

XCS0

3

6

5

7

9

XVA

10

XCB

15

XUB

14

XVB

13

XCA

12

XUA

11

18

17

16

19

20

23

XAUR

1

2

21

22

8

XBLK

3

XTIP

4

7

9

18

17

16

19

20

XADE

0

6

5

13

12

11

10

14

15

XSTR

X:$FFDF

XCS1

4

Reserved bit

AA0607k