9 tcs transmitter relative timing (trel)—bit 9, Tcs transmitter relative timing (trel)—bit 9 -20, Figure 6-12 – Motorola DSP56012 User Manual

Page 198: Transmitter clock polarity (tckp) programming -20, Figure 6-13, Transmitter relative timing (trel) programming -20

6-20

DSP56012 User’s Manual

MOTOROLA

Serial Audio Interface

Serial Audio Interface Programming Model

6.3.4.9

TCS Transmitter Relative Timing (TREL)—Bit 9

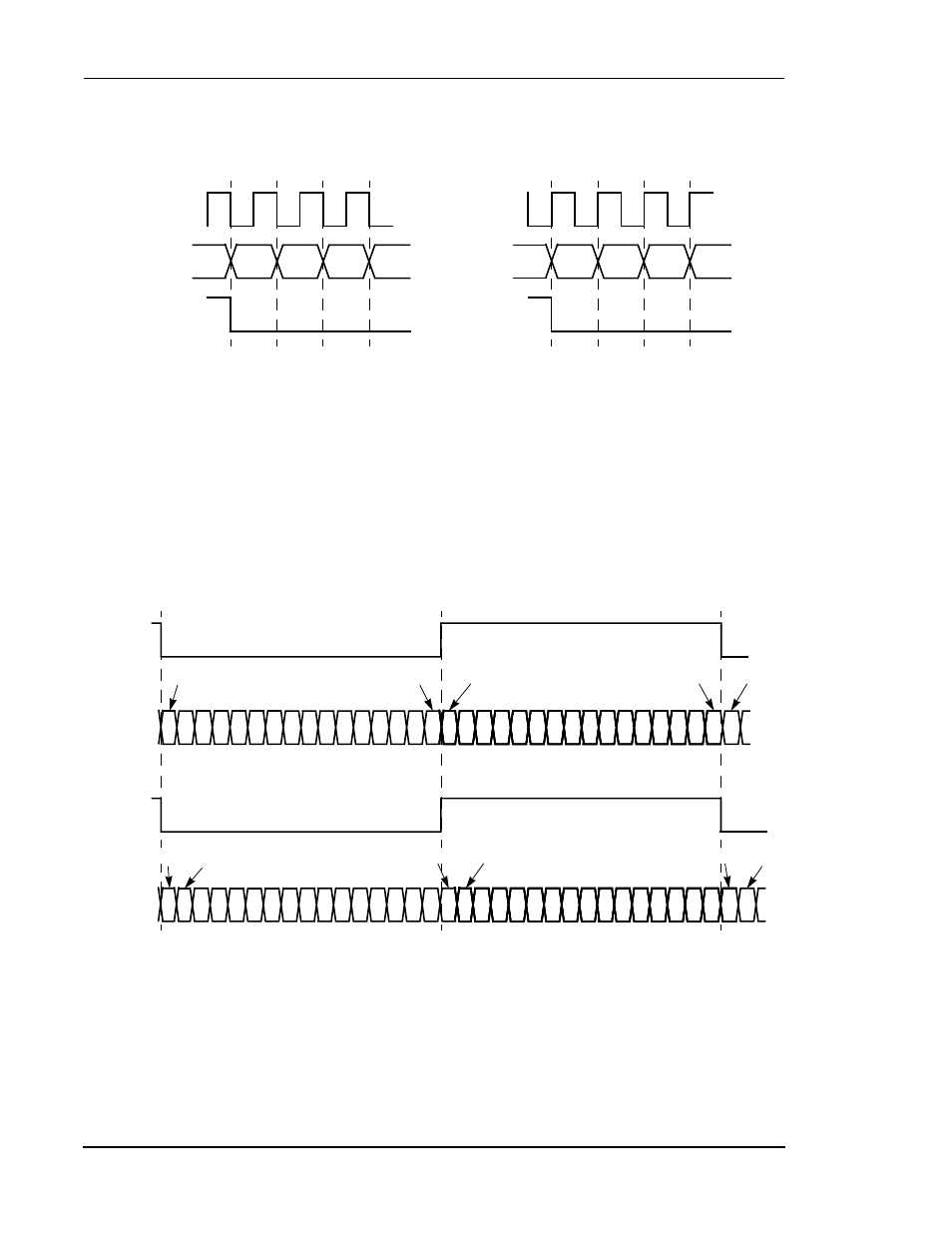

The read/write Transmitter Relative timing (TREL) control bit selects the relative

timing of the WST signal in reference to the serial data output lines (SDOx). When

TREL is cleared, the transition of WST, indicating the start of a data word, occurs

together with the first bit of that data word. When TREL is set, the transition of WST

occurs one serial clock cycle earlier (together with the last bit of the previous data

word), as required by the I

2

S format (see Figure 6-13).The TREL bit is cleared during

hardware reset and software reset.

6.3.4.10

TCS Transmitter Data Word Expansion (TDWE)—Bit 10

The read/write Transmitter Data Word Expansion (TDWE) control bit selects the

method used to expand a 24-bit data word to 32 bits during transmission. When

TDWE is cleared, after transmitting the 24-bit data word from the transmit data

Figure 6-12 Transmitter Clock Polarity (TCKP) Programming

Figure 6-13 Transmitter Relative Timing (TREL) Programming

SDO

SCKT

TCKP = 0

SDO

SCKT

TCKP = 1

WST

WST

AA0438k

MSB

LSB

LSB MSB

SDO

WST

MSB

Left

Right

MSB

LSB

LSB MSB

SDO

WST

MSB

Left

Right

LSB

TREL = 0

TREL = 1

AA0439