S.h.i, Programming reference – Motorola DSP56012 User Manual

Page 258

B-26

DSP56012 User’s Manual

MOTOROLA

Programming Reference

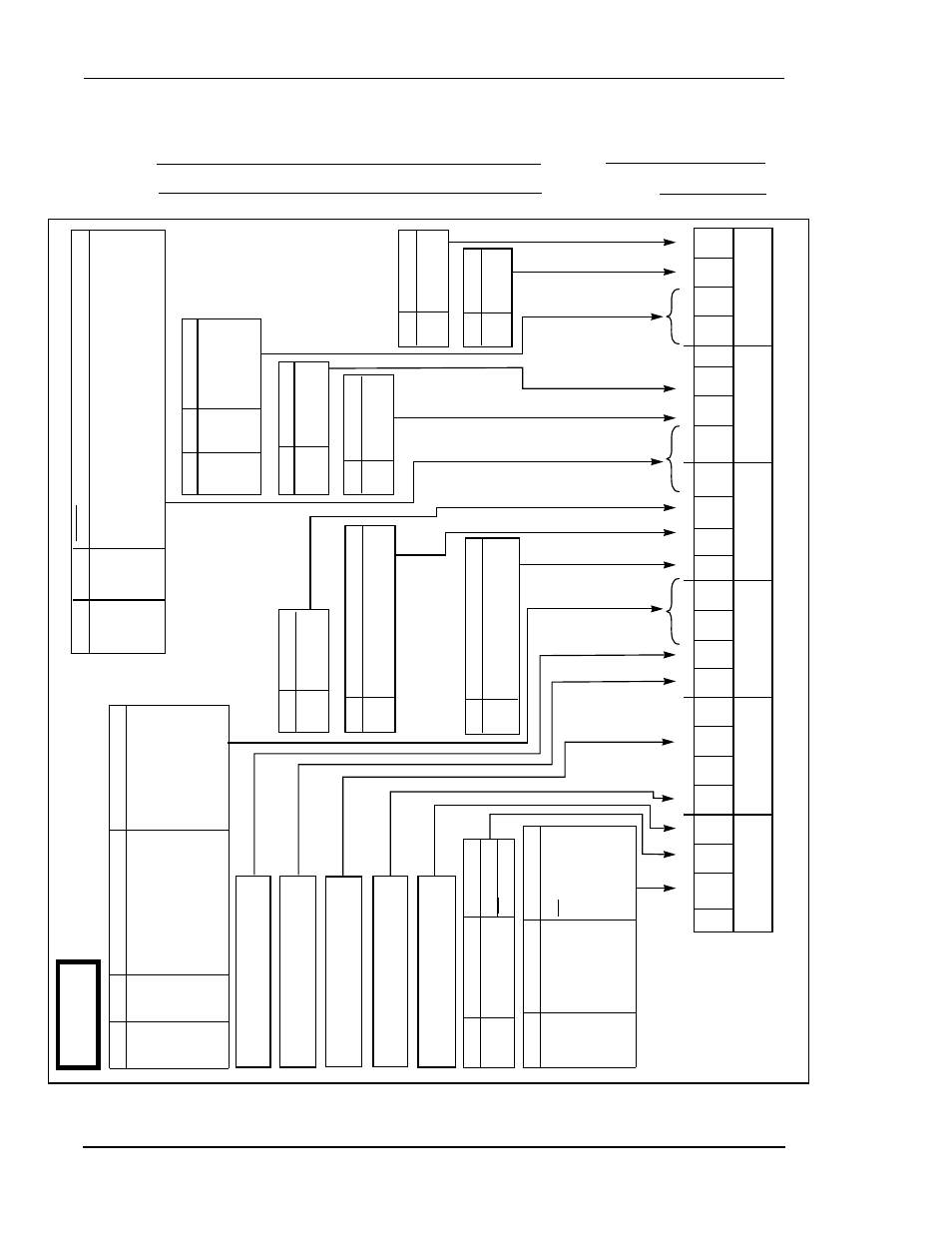

S.H.I.

*

= Reserved, write as 0

1

5

1

4

1

3

1

2

1

1

1

0

9876

5

4

3210

HRQE0

HFIF0

HM1

HM0

HI

2

C

HEN

SHI Control/Status

X:$FFF1

Reset = $008200

Register (HCSR)

19

18

17

16

23

22

21

20

HRFF

HROE

HBUSY

*

0

HMST

*

0

HTIE

HBIE

HIDLE

HRQE1

HTDE

HTUE

HRIE1

HRIE0

HRNE

HBER

HEN

Description

0

SHI disabled

1

SHI enabled

HI

2

C

Result

0

SPI mode

1I

2

C mode

HM1

HM0

Description

0

0

8 bit data

0

1

16 bit data

1

0

24 bit data

1

1

Reserved

HFIFO

Description

0

1

level FIFO

1

10 level

HMST

Result

0

Slave mode

1

Master mode

HRQE1

HRQE0

HREQ

Pin Operation

0

0

High impedance

0

1

Asserted if IOSR ready to receive new word

1

0

Asserted if IOSR ready to transmit new word

11

I

2

C: Asserted if IOSR ready to transmit or receive

SPI: Asserted if OISR ready to transmit and receive

HIDLE

Description

0

Bus busy

1

Stop event

HBIE

Description

0

Bus Error Interrupt disabled

1

Bus Error Interrupt enabled

HTIE

Description

0

Transmit Interrupt disabled

1

Transmit Interrupt activated

Host Transmit Underrun Error

Read Only Status Bit

Host Transfer Data Empty

Read Only Status Bit

Host Receive FIFO Not Empty

Read Only Status Bit

Host Receive FIFO Full

Read Only Status Bit

Host Receive Overrun Error

Read Only Status Bit

*

0

HBER

I

2

C SPI

Mode

0

No error

No error

1

No acknowledge

SS

asserted

HBUSY

I

2

C SPI

Mode

0

Stop event

Not Busy

1

SHI detects

Start

SS

detected

(Slave)

-OR-

HTX/IOSR not

empty (master)

HRIE1

HRIE0

Interrupt

Condition

00

1

0

1

disabled

Receive FIFO not empty

Receive Overrun Error

reserved

Receive FIFO full

Receive Overrun Error

n.a.

HRNE=1 & HROE=0

HROE=1

n.a.

HRFF=1 & HROE=0

HROE=1

0

1

1

Application:

Date:

Programmer:

Sheet 3 of 3

SHI Host Control/Status Register (HCSR)

*

0