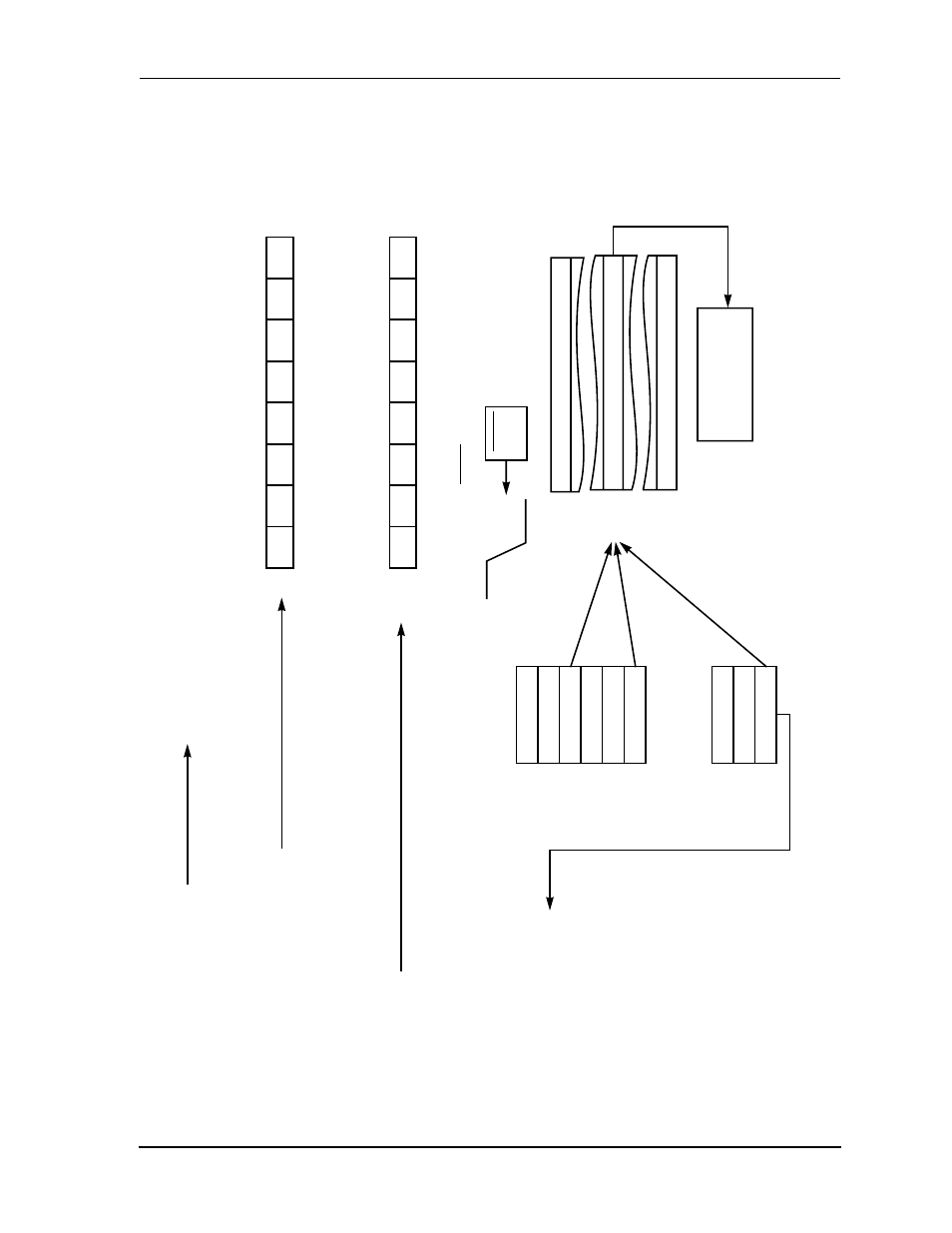

Figure437 host to dsp dma procedure, Figure 4-37, Host to dsp dma procedure -63 – Motorola DSP56012 User Manual

Page 143: Figure 4-37 host to dsp dma procedure, Parallel host interface host interface (hi)

Parallel Host Interface

Host Interface (HI)

MOTOROLA

DSP56012 User’s Manual

4-63

Figure 4-37

Host to DSP DMA Procedure

WRITE ICR

HOST PR

OCESSOR

X:$FFE8

HOST CONTR

OL

REGISTER (HCR)

P:$007E

A

V

AILABLE FOR HOST COMMAND

F

AST INTERR

UPT

OR

LONG INTERR

UPT

P:$0000

HOST TRANSMIT

D

A

T

A

VECT

OR

P:$0032

1.

PR

OGRAM DMA CONTR

OLLER.

—ST

AR

T ADDRESS

—BYTE COUNT

—TRANSFER DIRECTION

—ST

AR

T DMA CHANNEL

TXH

TXM

TXL

TXH

TXM

TXL

•

•

•

TXH

TXM

TXL

01

10

11

01

10

11

01

10

11

DSP56012

DMA CONTR

OLLER

2.

INITIALIZE DSP56012 HOST INTERF

A

CE.

—MODE 24 BIT DMA

—HOST T

O

DSP

—USE INIT BIT

T

O

:

SET TXDE

CLEAR HRDF

LO

AD DMA COUNTER

5.

HOST IS FREE

T

O

PERFORM

O

THER

T

ASKS (i.e

., DSP

T

O

HOST

TRANSFER ON A POLLED BASIS).

8.

TERMINA

TE DMA CHANNEL.

9.

TERMINA

TE DSP DMA MODE BY

CLEARING HM1, HM0, AND

TREQ.

7.

DMA CONTR

OLLER INTERR

UPTS HOST

WHEN

TRANSFERS ARE DONE.

HOREQ

PIN

6.

DMA CONTR

OLLER PERFORMS READS

.

$0

INTERR

UPT

CONTR

OL

REGISTER (ICR)

4.

ASSER

T HOREQ

T

O

ST

AR

T DMA

TRANSFER.

interr

upt VECT

OR T

ABLE

3.

TELL DSP56012

—WHERE

T

O

ST

ORE D

A

T

A

(i.e

., PR

OGRAM

ADDRESS REGISTER R7).

—ENABLE INTERR

UPT HRIE (CAN BE

DONE

WITH A HOST COMMAND).

1

HF1

HF0

1

0

70

1

0

6

5

432

1

0

INIT

HM1

HM0

TREQ

RREQ

0

HF3

HF2

HTIE

1

70

0

0

6

5

432

1

HCIE

HRIE

AA0343.11

Note: When using the SAI and DAX

peripherals, do not use interrupt vector

addresses P:$0040–$004A, $0050,

$0052, and $0056.