Figure 4-10, Host processor programming model–host side -23 – Motorola DSP56012 User Manual

Page 103

Parallel Host Interface

Host Interface (HI)

MOTOROLA

DSP56012 User’s Manual

4-23

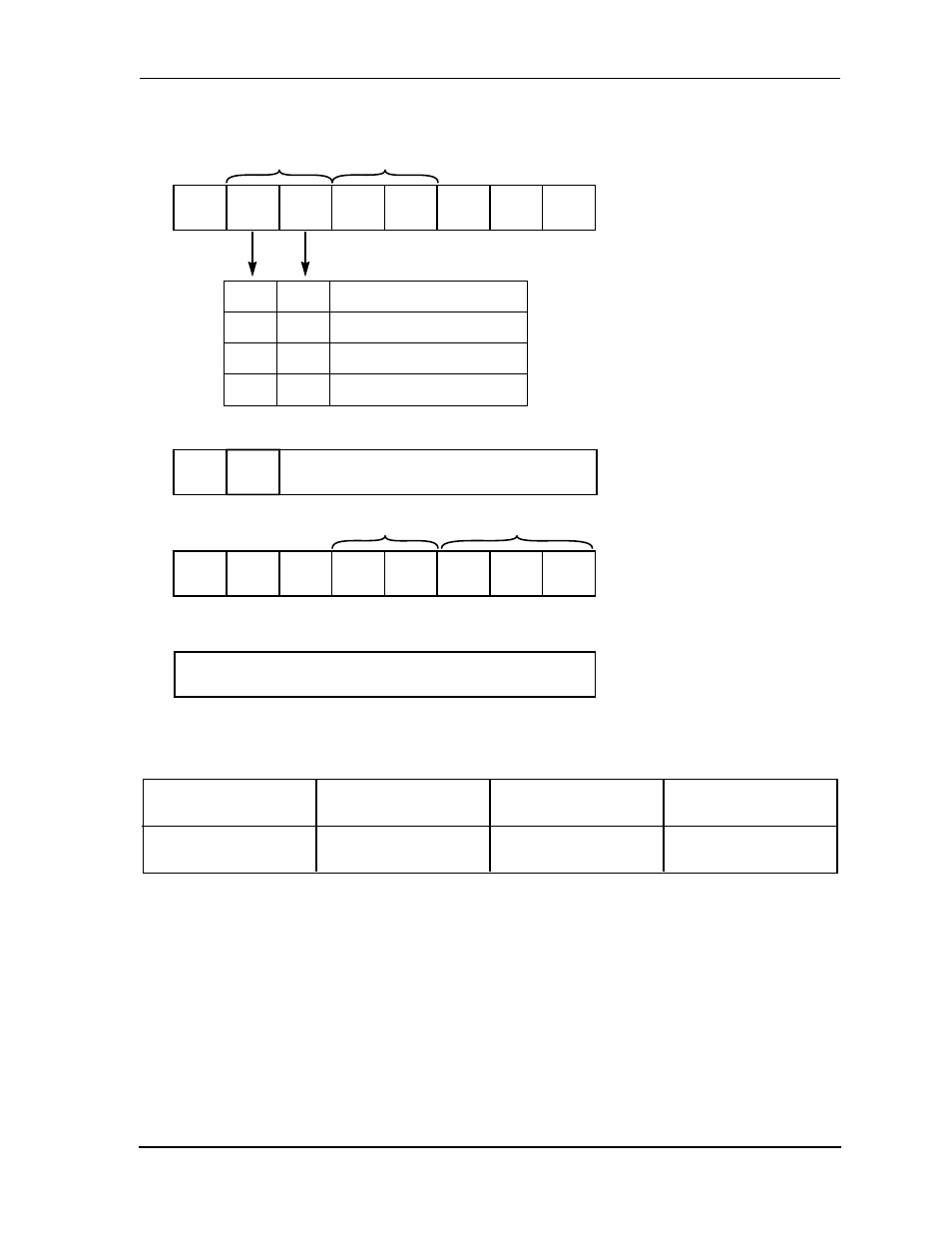

Figure 4-10 Host Processor Programming Model–Host Side

Interrupt Vector Number

($0F)

0 0 0 0 0 0 0 0

RXH

Receive High Byte

RXM

Receive Middle Byte

Not Used

TXH

Transmit High Byte

TXM

Transmit Middle Byte

Note:

1.

The numbers in parentheses are reset initialization values.

0

0

Interrupt Mode (DMA Off)

0

1

24-Bit DMA Mode

1

0

GPIO-Bit DMA Mode

1

1

8-Bit DMA Mode

Host Vector

($17)

Status

Flags

RXL

Receive Low Byte

TXL

Transmit Low Byte

Receive Byte Registers (RXH:RXM:RXL)

(Read Only)

Transmit Byte Registers (TXH:TXM:TXL)

(Write Only)

$2

Interrupt Status Register (ISR)

(Read Only)

HOREQ

(0)

0

HF3

(0)

HF2

(0)

TRDY

(1)

TXDE

(1)

RXDF

(0)

7

0

31

24 23

0

7

0 7

0

0 7

0 7

8 7

16 15

$7

$6

$5

$4

$3

Interrupt Vector Register (IVR)

(Read/Write)

7

0

$1

Command Vector Register (CVR)

(Read/Write)

HC

(0)

0

7

0

DMA

(0)

Flags

Modes

$0

Interrupt Control Register (ICR)

(Read/Write)

INIT

(0)

0

HF1

(0)

HF0

(0)

TREQ

(1)

RREQ

(0)

7

0

HM1

(0)

HM0

(0)

5

AA0319k