2 i2c data transfer formats, Figure510 i2c bus protocol for host write cycle, Figure511 i2c bus protocol for host read cycle – Motorola DSP56012 User Manual

Page 170: Figure 5-10, Figure 5-11, C data transfer formats

5-22

DSP56012 User’s Manual

MOTOROLA

Serial Host Interface

Characteristics Of The I

2

C Bus

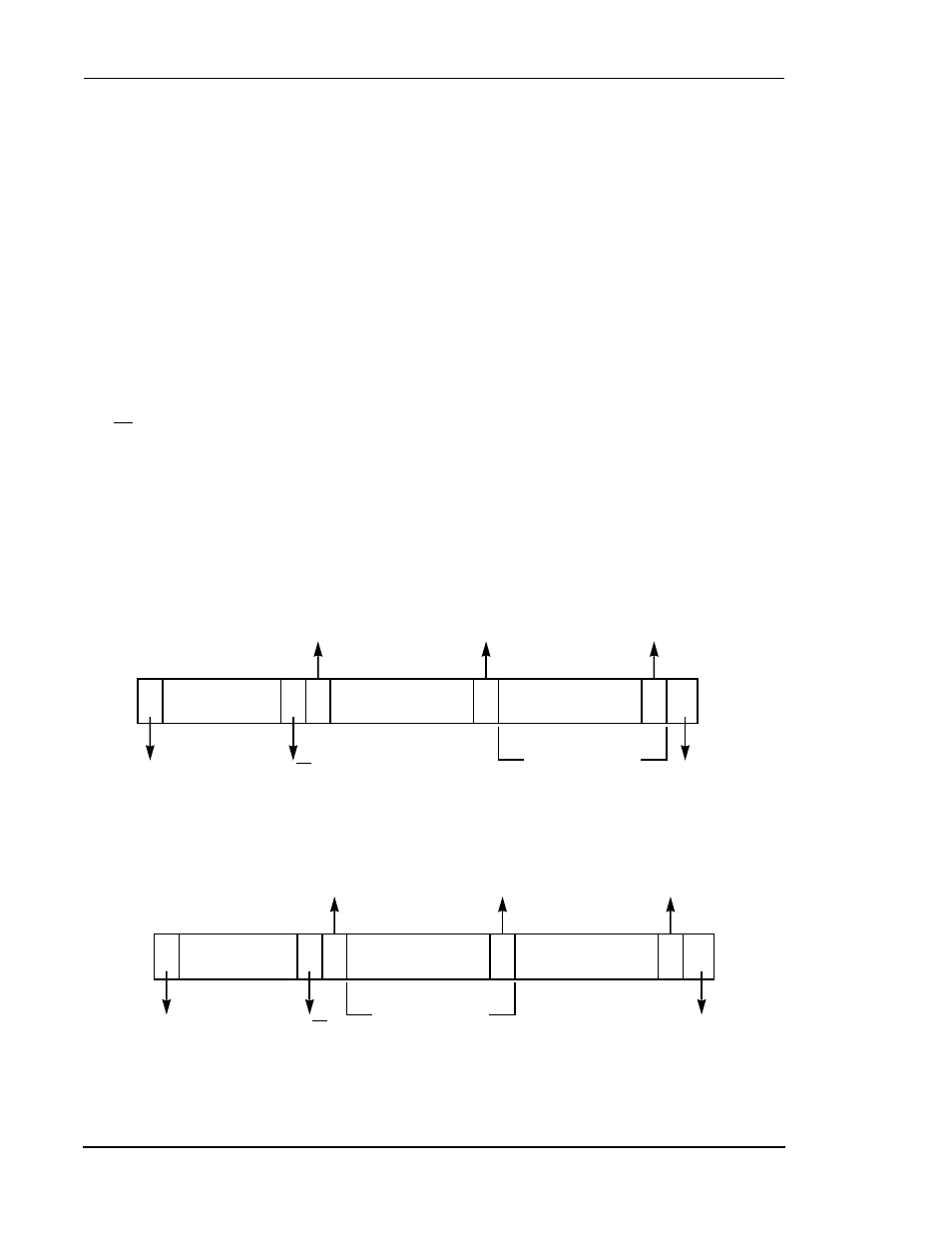

generation of the stop event. Handshaking may also be accomplished by use of the

clock synchronizing mechanism. Slave devices can hold the SCL line low, after

receiving and acknowledging a byte, to force the master into a wait state until the

slave device is ready for the next byte transfer. The SHI supports this feature when

operating as a master device and will wait until the slave device releases the SCL line

before proceeding with the data transfer.

5.6.2

I

2

C Data Transfer Formats

I

2

C bus data transfers follow the following format: after the start event, a slave device

address is sent. This address is 7 bits wide, the eighth bit is a data direction bit

(R/W)

;

‘0’ indicates a transmission (write), and ‘1’ indicates a request for data (read).

A data transfer is always terminated by a stop event generated by the master device.

However, if the master device still wishes to communicate on the bus, it can generate

another start event, and address another slave device without first generating a stop

event (this feature is not supported by the SHI when operating as an I

2

C master

device). This method is also used to provide indivisible data transfers. Various

combinations of read/write formats are illustrated in

Figure 5-10 I

2

C Bus Protocol For Host Write Cycle

Figure 5-11 I

2

C Bus Protocol For Host Read Cycle

S

A

A

0

Slave Address

R/W

S, P

A

Start

Start or

Bit

Stop Bit

Slave Device

ACK from

Slave Device

ACK from

Slave Device

ACK from

N = 0 to M

Data Bytes

First Data Byte

Data Byte

AA0425

S

A

A

1

Slave Address

R/W

P

1

Start

Stop

Bit

Bit

Slave Device

ACK from

Master Device

ACK from

No ACK

Data Byte

N = 0 to M

Data Bytes

Last Data Byte

from Master Device

AA0426