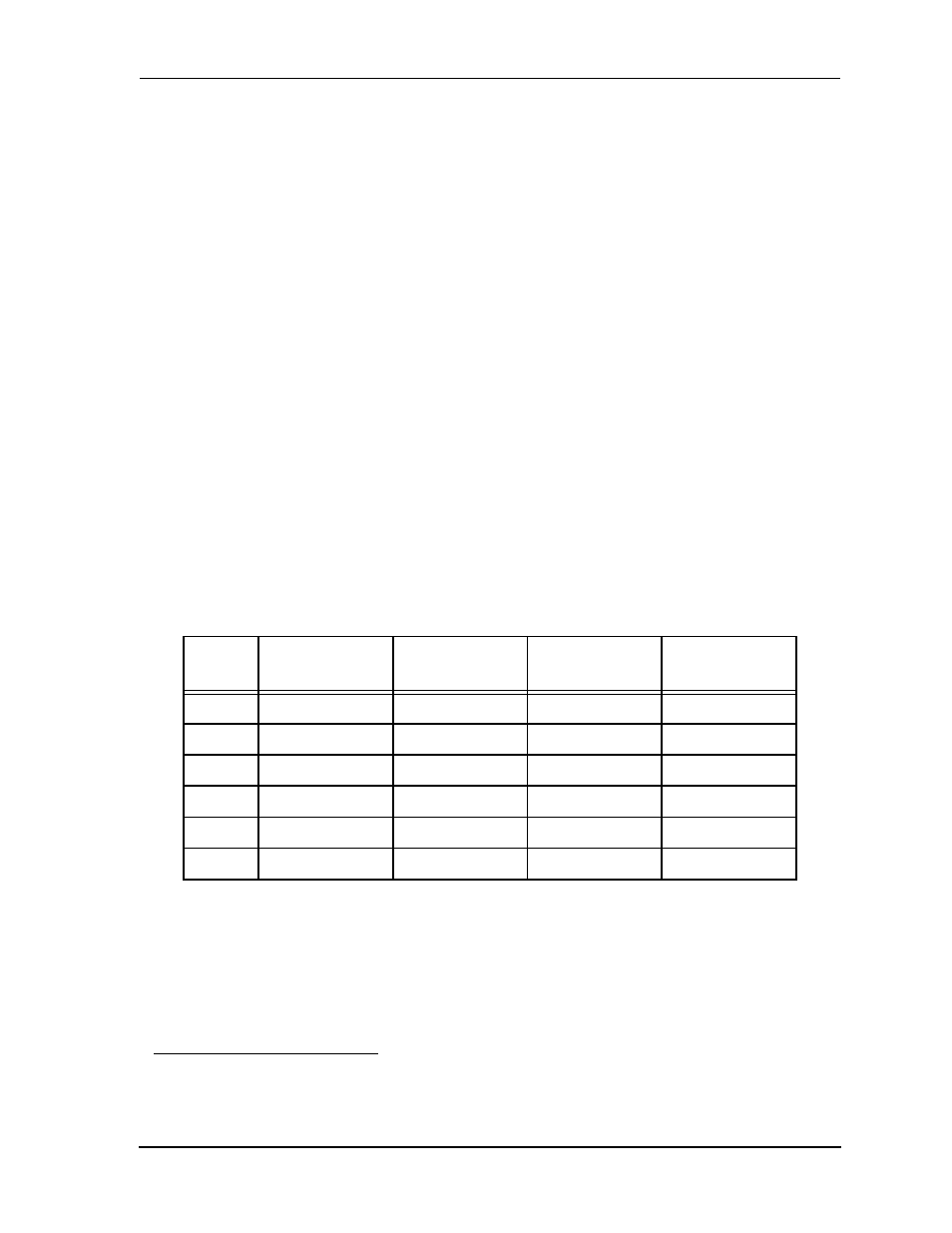

Table12 dsp56012 internal memory configurations, Table 1-2, Dsp56012 internal memory configurations -7 – Motorola DSP56012 User Manual

Page 27

Overview

DSP56012 Features

MOTOROLA

DSP56012 User’s Manual

1-7

– PLL-based clocking with a wide range of frequency multiplications (1 to

4096) and power saving clock divider (2

i

: i = 0 to 15), which reduces clock

noise

– Four 24-bit internal data buses and three 16-bit internal address buses for

simultaneous accesses to one program and two data memories

• Memory

– Modified Harvard architecture allows simultaneous access to program and

data memories

– 15360

×

24-bit on-chip Program ROM

1

– 4096

×

24-bit on-chip X-data RAM and 3584

×

24-bit on-chip X-data ROM*

– 4352

×

24-bit on-chip Y-data RAM and 2048

×

24-bit on-chip Y-data ROM*

– 256

×

24-bit on-chip Program RAM and 32

×

24-bit bootstrap ROM

– As much as 2304

×

24 bits of X- and Y-data RAM can be switched to

Program RAM, giving a total of 2560

×

24 bits of Program RAM

lists the memory configurations of the DSP56012.

• Peripheral and Support Circuits

– SAI includes:

• Two receivers and three transmitters

• Master or slave capability

• I

2

S, Sony, and Matshushita audio protocol implementations

1.

These ROMs may be factory programmed with data/program provided by the application developer.

Table 1-2

DSP56012 Internal Memory Configurations

No Switch

(PEA=0, PEB=0)

Switch A

(PEA=1, PEB=0)

Switch B

(PEA=0, PEB=1)

Switch A+B

(PEA=1, PEB=1)

P: RAM

0.25 K

1.0 K

1.75 K

2.5 K

X: RAM

4.0 K

3.25 K

3.25 K

2.5 K

Y: RAM

4.25 K

4.25 K

3.5 K

3.5 K

P: ROM

15 K

15 K

15 K

15 K

X: ROM

3.5 K

3.5 K

3.5 K

3.5 K

Y: ROM

2.0 K

2.0 K

2.0 K

2.0 K