Figure435 hi hardware–dma mode, Figure 4-35, Hi hardware–dma mode -60 – Motorola DSP56012 User Manual

Page 140: Figure 6-10, Figure 4-35 hi hardware–dma mode, Parallel host interface host interface (hi)

4-60

DSP56012 User’s Manual

MOTOROLA

Parallel Host Interface

Host Interface (HI)

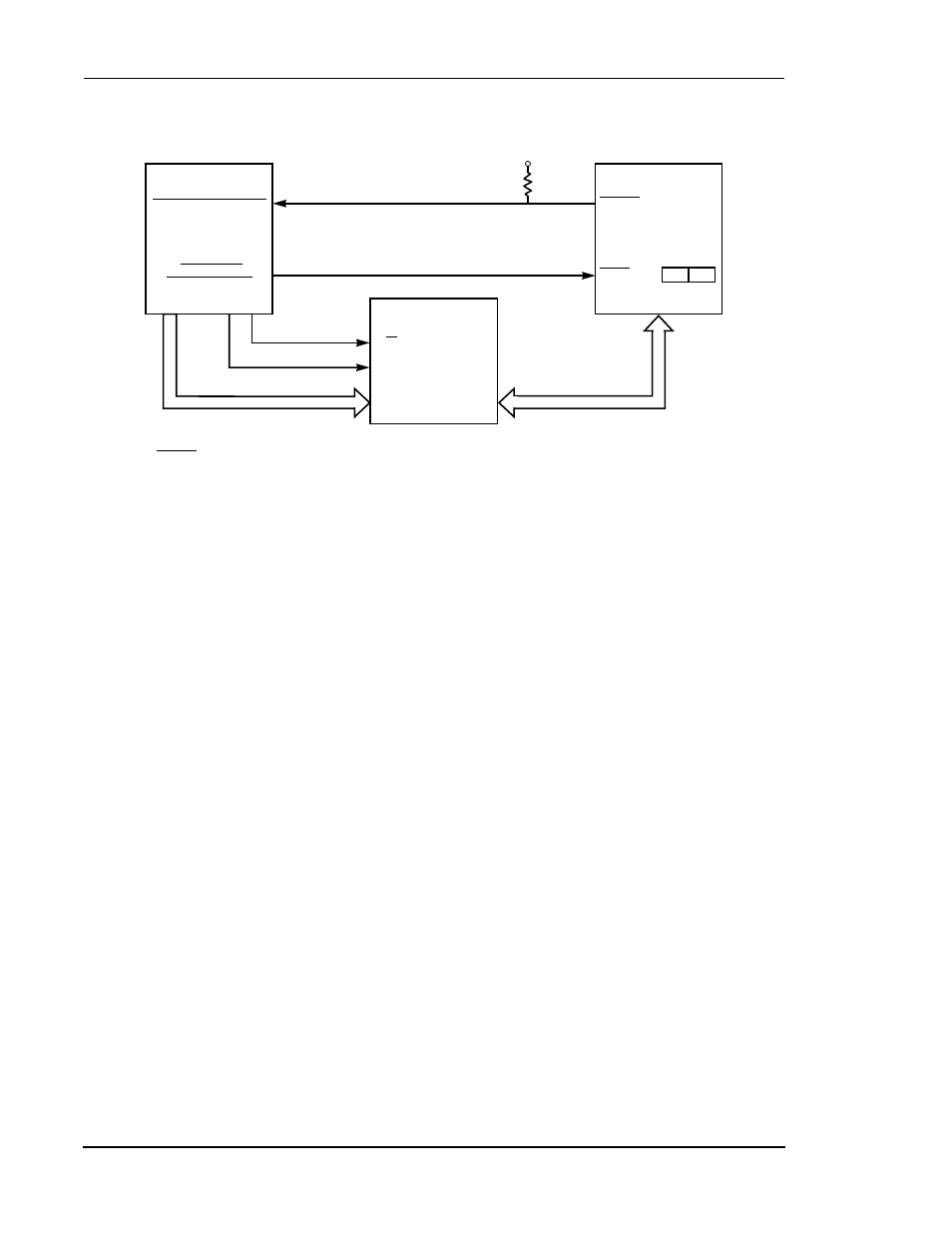

Figure 4-35 HI Hardware–DMA Mode

+5 V

DMA

CONTROLLER

TRANSFER REQUEST

TRANSFER

ACKNOWLEDGE

DSP56012

HOST INTERFACE

HOREQ

HACK

INTERNAL

ADDRESS

COUNTER

H[7:0]

1 K

MEMORY

R/W

CONTROL

ADDRESS

DATA

Characteristics of HI DMA Mode

• The HOREQ pin is NOT available for host processor interrupts.

• TREQ and RREQ select the direction of DMA transfer.

—DMA to DSP56012

—DSP56012 to DMA

—Simultaneous bidirectional DMA transfers are not permitted.

• Host processor software polled transfers are permitted in the opposite direction of the DMA transfer.

• 8-, 16-, or 24-bit transfers are supported.

• 16-, or 24-bit transfers reduce the DSP interrupt rate by a factor of 2 or 3, respectively.

AA0341k