Figure46 i/o port b configuration, 4 host interface (hi), Host interface (hi) -9 – Motorola DSP56012 User Manual

Page 89: Figure 4-6, I/o port b configuration -9, Is optional and can be changed as, Sheets for the timing specifications

Parallel Host Interface

Host Interface (HI)

MOTOROLA

DSP56012 User’s Manual

4-9

Note:

The Port B GPIO timing differs from the timing of the GPIO peripheral. Please

refer to the

DSP56012 Technical Data

sheets for the timing specifications.

4.4

HOST INTERFACE (HI)

The Host Interface (HI) is a byte-wide, full-duplex, double-buffered, parallel port

that can be connected directly to the data bus of a host processor to be used primarily

as a parallel data transfer port. The host processor can be any of a number of

industry-standard microcomputers or microprocessors, another DSP, or Direct

Memory Address (DMA) devices because this interface looks like static memory to

those devices. The HI is asynchronous and consists of two banks of registers—one

bank accessible to the host processor and a second bank accessible to the DSP Central

Processing Unit (CPU) (see

Note:

Unlike other DSPs in this Motorola family, this device uses the SHI for a host

control interface, and the HI as a high-speed parallel data transfer interface.

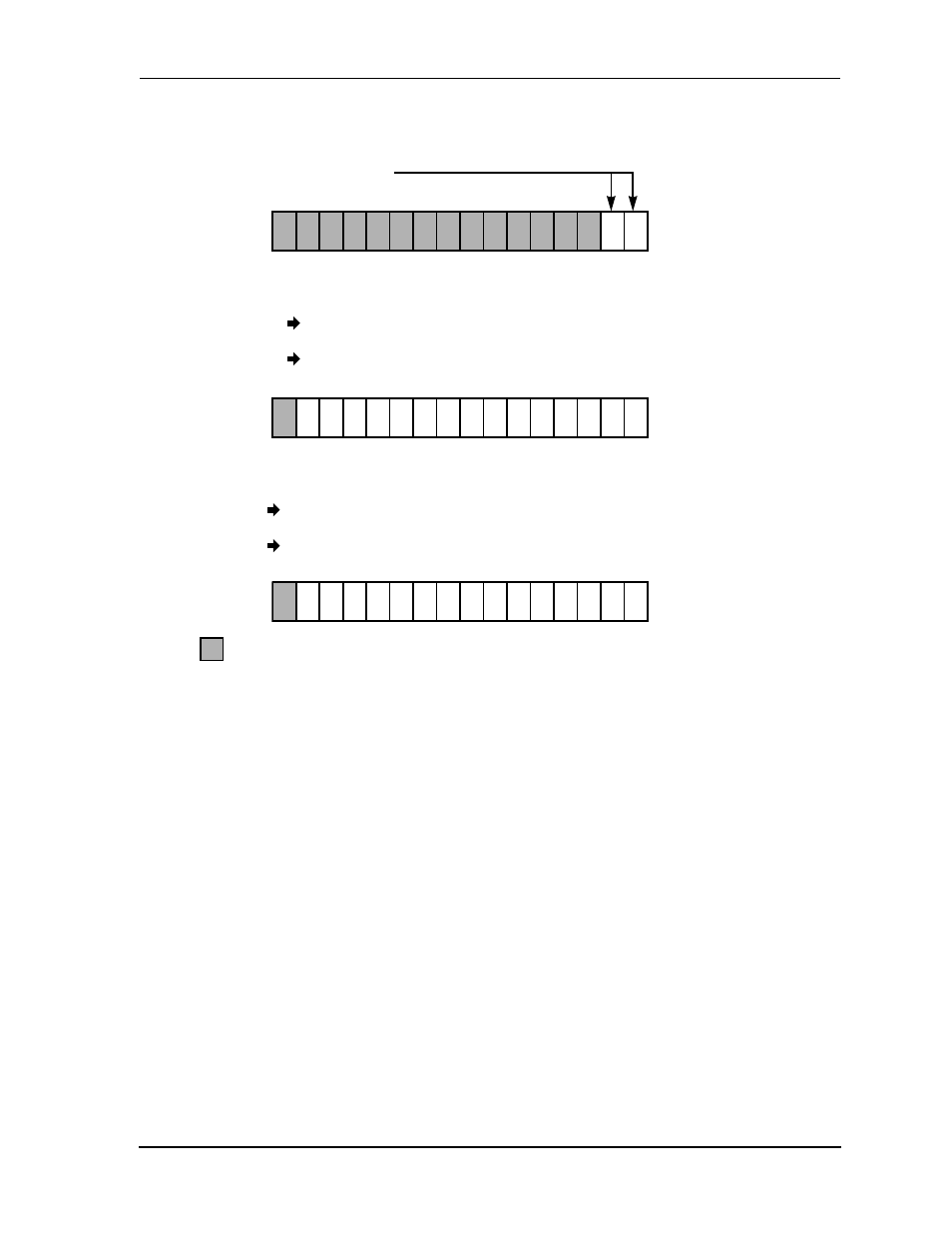

Figure 4-6 I/O Port B Configuration

BC

1

BC

0

15

0

X:$FFEC

Port B

Control Register (PBC)

BD

14

BD

13

BD

12

BD

11

BD

10

BD

9

BD

8

BD

7

BD

6

BD

5

BD

4

BD

3

BD

2

BD

1

BD

0

15

0

Step 1. Activate Port B For General Purpose I/O:

Write 0s to Bits 0 And 1

Step 2. Set Individual Pins To Input Or Output:

BDxx = 0

or

BDxx = 1

Input

Output

Reserved; write as 0

X:$FFED

Port B Data Direction

Register (PBDDR)

Step 3. Write Or Read Data:

PDxx

or

PDxx

Input if BDxx = 0

Output if BDxx = 1

PB

14

PB

13

PB

12

PB

11

PB

10

PB

9

PB

8

PB

7

PB

6

PB

5

PB

4

PB

3

PB

2

PB

1

PB

0

15

0

X:$FFEE

Port B Data

register (PBD)

AA0312.11