Figure411 hi register map, 3 interrupt control register (icr), 1 icr receive request enable (rreq)—bit 0 – Motorola DSP56012 User Manual

Page 104: 2 icr transmit request enable (treq)—bit 1, Interrupt control register (icr) -24, Icr receive request enable (rreq)—bit 0 -24, Icr transmit request enable (treq)—bit 1 -24, Figure 4-11, Hi register map -24

4-24

DSP56012 User’s Manual

MOTOROLA

Parallel Host Interface

Host Interface (HI)

4.4.5.3

Interrupt Control Register (ICR)

The Interrupt Control Register (ICR) is an 8-bit read/write control register used by

the host processor to control the HI interrupts and flags. The ICR cannot be accessed

by the DSP CPU. The ICR is a read/write register that allows the use of bit

manipulation instructions on control register bits. The control bits are described in

the following paragraphs.

4.4.5.3.1

ICR Receive Request Enable (RREQ)—Bit 0

The Receive Request Enable (RREQ) bit is used to control the HOREQ pin for host

receive data transfers. In Interrupt mode (DMA off), RREQ is used to enable

interrupt requests via the external HI Request (HOREQ) pin when the Receive Data

Register Full (RXDF) status bit in the ISR is set. When RREQ is cleared, RXDF

interrupts are disabled. When RREQ is set, the external HOREQ pin will be asserted

if RXDF is set.

In DMA modes, RREQ must be set or cleared by software to select the direction of

DMA transfers. Setting RREQ sets the direction of DMA transfer to be DSP-to-host

and enables the HOREQ pin to request data transfer.

Note:

Hardware reset, software reset, individual reset, and Stop clear RREQ.

4.4.5.3.2

ICR Transmit Request Enable (TREQ)—Bit 1

The Transmit Request enable (TREQ)

bit is used to control the HOREQ pin for host

transmit data transfers. In Interrupt mode (DMA off), TREQ is used to enable

interrupt requests via the external HOREQ pin when the Transmit Data register

Empty (TXDE) status bit in the ISR is set. When TREQ is cleared, TXDE interrupts are

disabled. When TREQ is set, the external HOREQ pin will be asserted if TXDE is set.

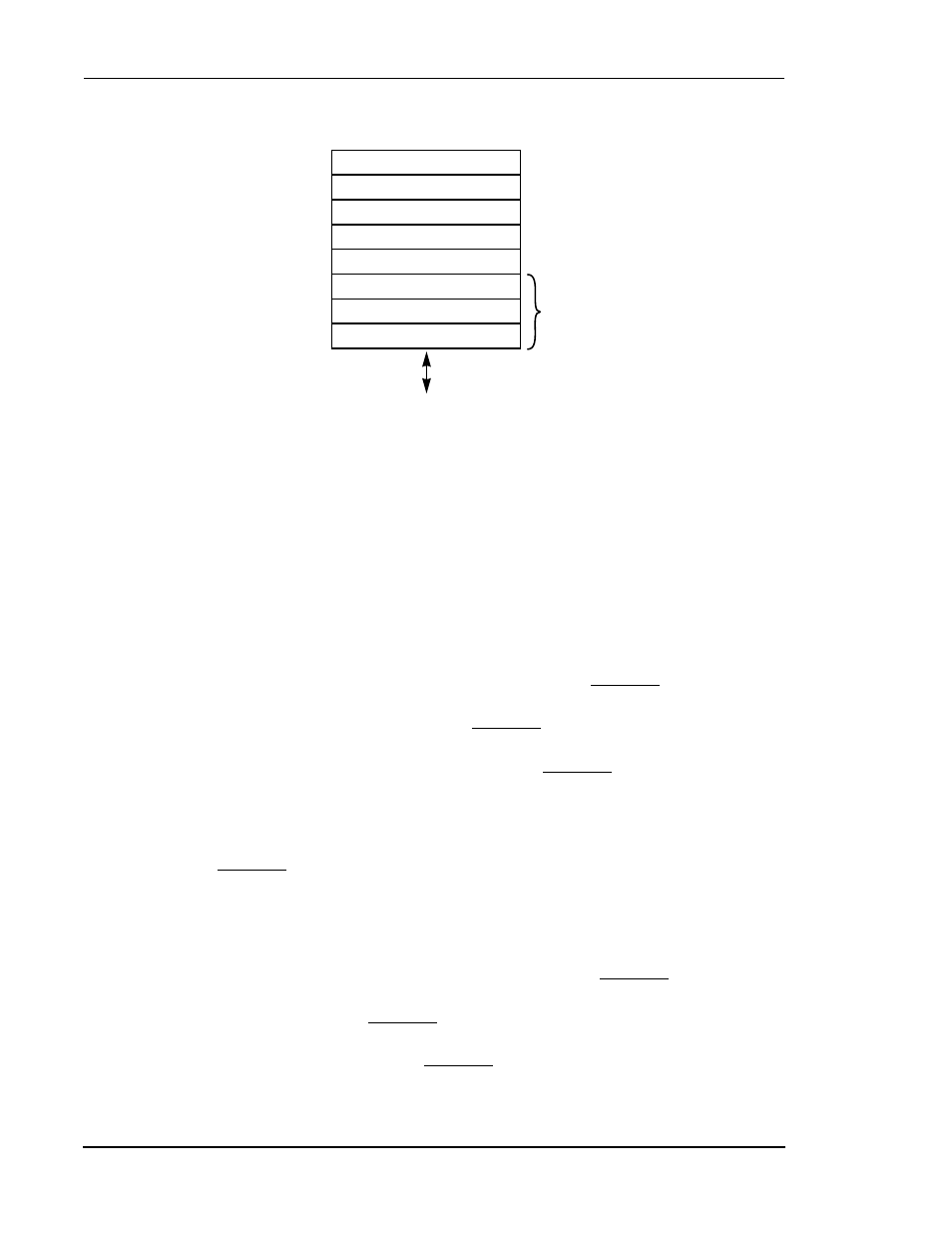

Figure 4-11 HI Register Map

AA0320k

$0

$1

$2

$3

$4

$5

$6

$7

Interrupt Control

Command Vector

Interrupt Status

Interrupt Vector

Unused

Receive/Transmit

Bytes

ICR

CVR

ISR

IVR

0 0 0 0 0 0 0 0

RXH/TXH

RXM/TXM

RXL/TXL

Host Address

HOA[2:0]

HI Data Bus

H[7:0]