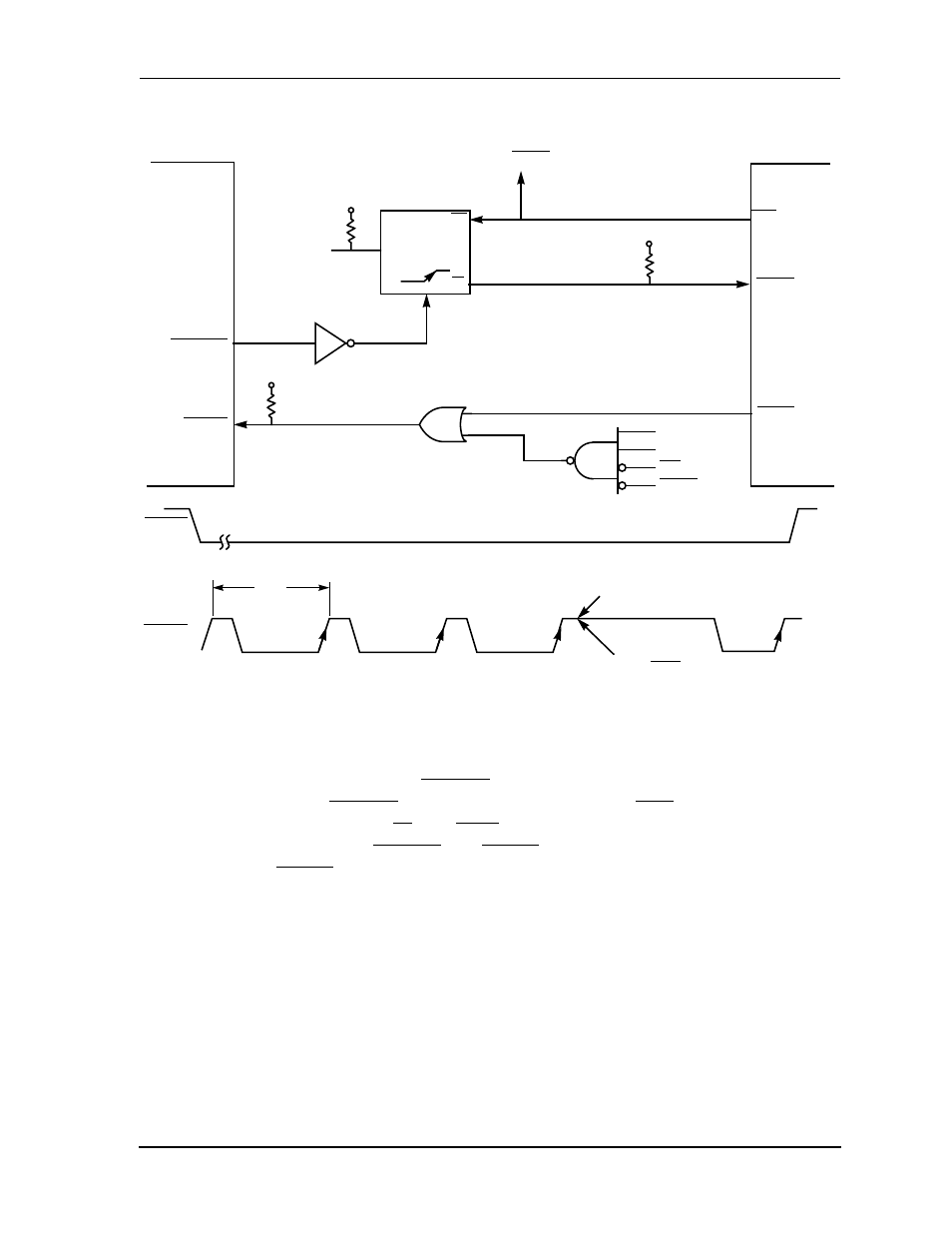

Figure417 dma transfer logic and timing, 5 servicing dma interrupts, Servicing dma interrupts -41 – Motorola DSP56012 User Manual

Page 121: Figure 4-17, Dma transfer logic and timing -41, Ipl2 in

Parallel Host Interface

Host Interface (HI)

MOTOROLA

DSP56012 User’s Manual

4-41

4.4.7.5

Servicing DMA Interrupts

When HM0

≠

0 and/or HM1

≠

0, HOREQ will be asserted to request a DMA

transfer. Generally the HOREQ pin will be connected to the REQ input of a DMA

controller. The HOA[2:0], HR/W, and HEN pins are not used during DMA transfers;

DMA transfers only use the HOREQ and HACK pins after the DMA channel has

been initialized. HACK is used to strobe the data transfer, as shown in

on page 4-41 where an MC68440 is used as the DMA controller. DMA transfers to

and from the HI are presented in more detail in

Section

Figure 4-17 DMA Transfer Logic and Timing

DMA ACK Gated Off

Fast Interrupt

To Transfer 24-bit Word

High

Byte

MC68440

IRQ

ACK0

+5 V

DSP56012

To IRQB

+5 V

+5 V

HOREQ

HACK

REQ0

CI

Q

D

Burst

REQ0

HACK

High

Byte

Middle

Byte

Low

Byte

1 DMA Cycle = 8T = 4 DMA Clock Cycles

Max. MC68440 Clock = 10 MHz = > T = 50 ns

8T

A0

A1

AS

OWN

AA0325k