Figure421 hi mode and init bits, 2 polling/interrupt controlled data transfer, Polling/interrupt controlled data transfer -45 – Motorola DSP56012 User Manual

Page 125: Figure 4-21, Hi mode and init bits -45

Parallel Host Interface

Host Interface (HI)

MOTOROLA

DSP56012 User’s Manual

4-45

4.4.8.2

Polling/Interrupt Controlled Data Transfer

Handshake flags are provided for polled or interrupt-driven data transfers. Because

the DSP interrupt response is sufficiently fast, most host microprocessors can load or

store data at their maximum programmed I/O (non-DMA) instruction rate without

testing the handshake flags for each transfer. If the full handshake is not needed, the

host processor can treat the DSP as fast memory, and data can be transferred between

the host and DSP at the fastest host processor rate. DMA hardware can be used with

the external host request and host acknowledge pins to transfer data at the maximum

DSP interrupt rate.

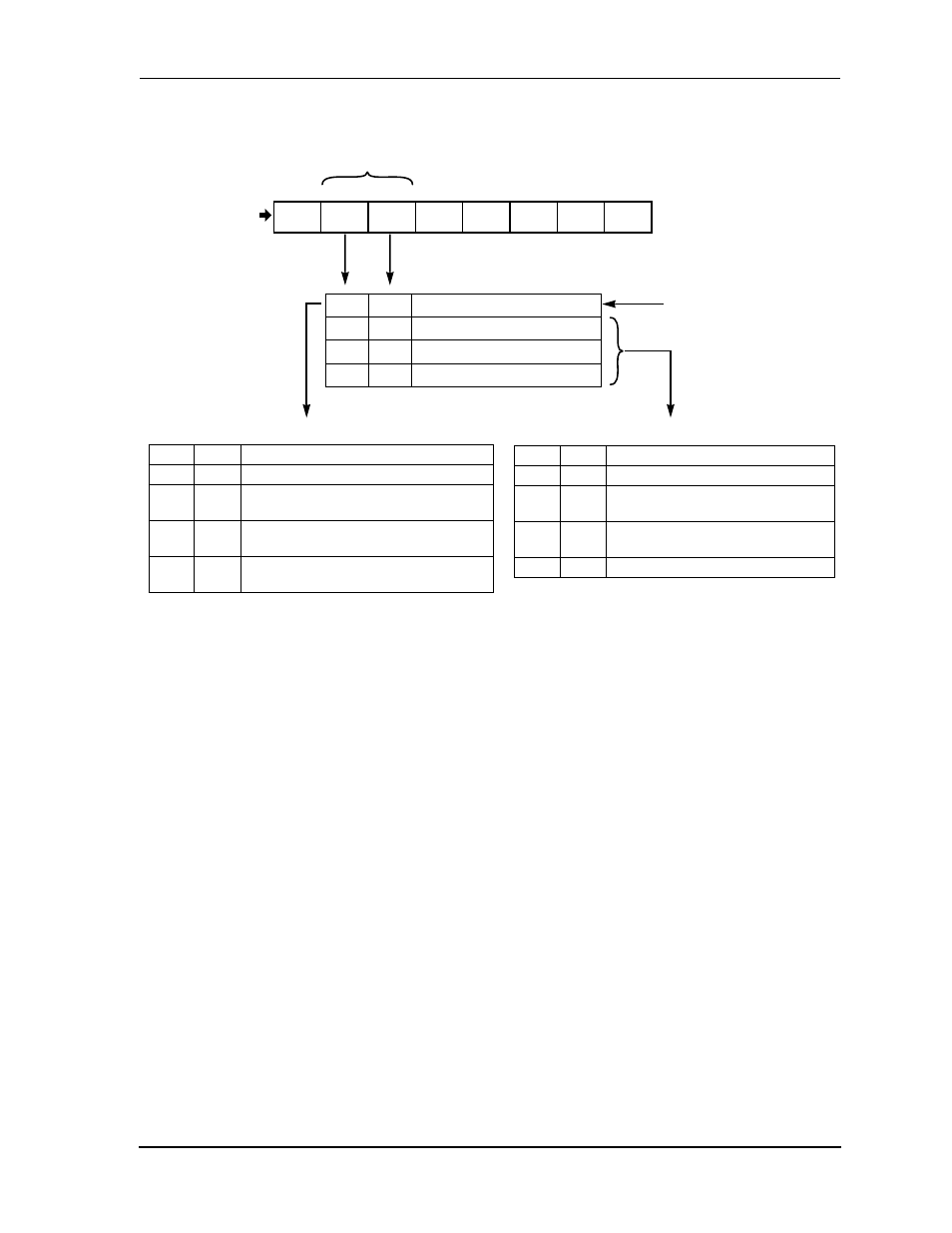

Figure 4-21 HI Mode and INIT Bits

TREQ RREQ

INIT Execution

0

0

INIT = 0; Address Counter = 00

0

1

INIT = 0; RXDF = 0; HTDE = 1;

Address Counter = 00

1

0

INIT = 0; TXDE = 1; HRDF = 0;

Address Counter = 00

1

1

INIT = 0; RXDF = 0; HTDE = 1: TXDE = 1;

HRDF = 0; Address Counter = 00

Modes

0

0

Interrupt Mode (DMA Off)

0

1

24-Bit DMA Mode

1

0

16-Bit DMA Mode

1

1

8-Bit DMA Mode

Reset Condition

Interrupt Mode (DMA Off)

TREQ RREQ

INIT Execution

0

0

INIT = 0; Address Counter = HM1, HM0

0

1

INIT = 0; RXDF = 0; HTDE = 1;

Address Counter = HM1, HM0

1

0

INIT = 0; TXDE = 1; HRDF = 0;

Address Counter = HM1, HM0

1

1

Undefined (Illegal)

DMA Mode

INIT is used by the host to force initialization of the HI hardware.

The HI hardware automatically clears INIT when the command is executed.

INIT is cleared by DSP RESET.

AA0329k

Interrupt Control Register

(ICR)

(Read/Write)

Host Sets

INIT Bit

HF1

HF0

TREQ RREQ

7

0

6

5

4

3

2

1

HM0

HM1

INIT

HF00