1 shi input/output shift register (iosr)—host side, Figure55 shi i/o shift register (iosr), 2 shi host transmit data register (htx)—dsp side – Motorola DSP56012 User Manual

Page 156: Shi host transmit data register (htx)—dsp side -8, Figure 5-5, Shi i/o shift register (iosr) -8

5-8

DSP56012 User’s Manual

MOTOROLA

Serial Host Interface

Serial Host Interface Programming Model

5.4.1

SHI Input/Output Shift Register (IOSR)—Host Side

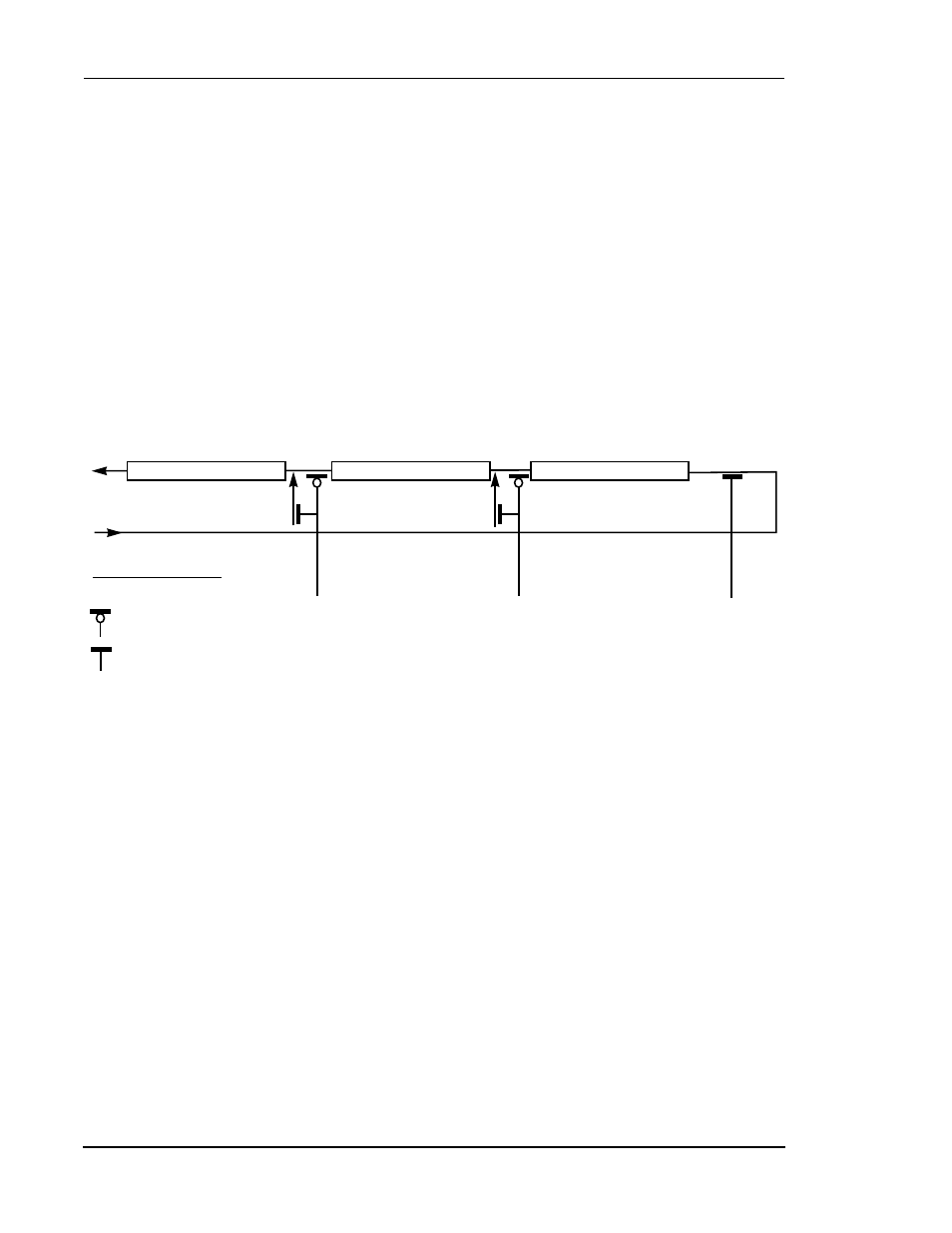

The variable length Input/Output Shift Register (IOSR) can be viewed as a

serial-to-parallel and parallel-to-serial buffer in the SHI. The IOSR is involved with

every data transfer in both directions (read and write). In compliance with the I

2

C

and SPI bus protocols, data is shifted in and out MSB first. In single-byte data transfer

modes, the most significant byte of the IOSR is used as the shift register. In 16-bit

data transfer modes, the two most significant bytes become the shift register. In 24-bit

transfer modes, the shift register uses all three bytes of the IOSR (see

Note:

The IOSR cannot be accessed directly either by the host processor or by the

DSP. It is fully controlled by the SHI controller logic.

5.4.2

SHI Host Transmit Data Register (HTX)—DSP Side

The Host Transmit data register (HTX) is used for DSP-to-Host data transfers. The

HTX register is 24 bits wide. Writing to the HTX register clears the HTDE flag. The

DSP may program the HTIE bit to cause a Host transmit data interrupt when HTDE

is set (see

5.4.6.10 HCSR Transmit-Interrupt Enable (HTIE)—Bit 11

Data should not be written to the HTX until HTDE is set in order to prevent

overwriting the previous data. HTX is reset to the empty state when in Stop mode

and during hardware reset, software reset, and individual reset.

In the single-byte data transfer mode the most significant byte of the HTX is

transmitted; in the double-byte mode the two most significant bytes, and in the

triple-byte mode all the HTX is transferred.

Figure 5-5 SHI I/O Shift Register (IOSR)

16

23

8

15

0

7

8-Bit Data

Mode

16-Bit Data

Mode

24-Bit Data

Mode

Mode of Operation

Stops Data When Data Mode is Selected

Passes Data When Data Mode is Selected

AA0420k