Table61 sai interrupt vector locations, Table62 sai internal interrupt priorities, 1 baud rate control register (brc) – Motorola DSP56012 User Manual

Page 187: Baud rate control register (brc) -9, Table 6-1, Sai interrupt vector locations -9, Table 6-2, Sai internal interrupt priorities -9

Serial Audio Interface

Serial Audio Interface Programming Model

MOTOROLA

DSP56012 User’s Manual

6-9

6.3.1

Baud Rate Control Register (BRC)

The serial clock frequency is determined by the control bits in the Baud Rate Control

register (BRC) as described in the following paragraphs. The BRC is illustrated in

Figure 6-4

on page 6-8. The maximum allowed internally generated bit clock

frequency is f

osc

/4 and the maximum allowed external bit clock frequency is f

osc

/3.

BRC bits should be modified only when the baud-rate generator is disabled (i.e.,

when both receiver and transmitter sections are defined as slaves or when both are in

the individual reset state); otherwise improper operation may result. When read by

the DSP, the BRC appears on the two low-order bytes of the 24-bit word, and the

high-order byte is read as 0s. The BRC is cleared during hardware reset and software

reset.

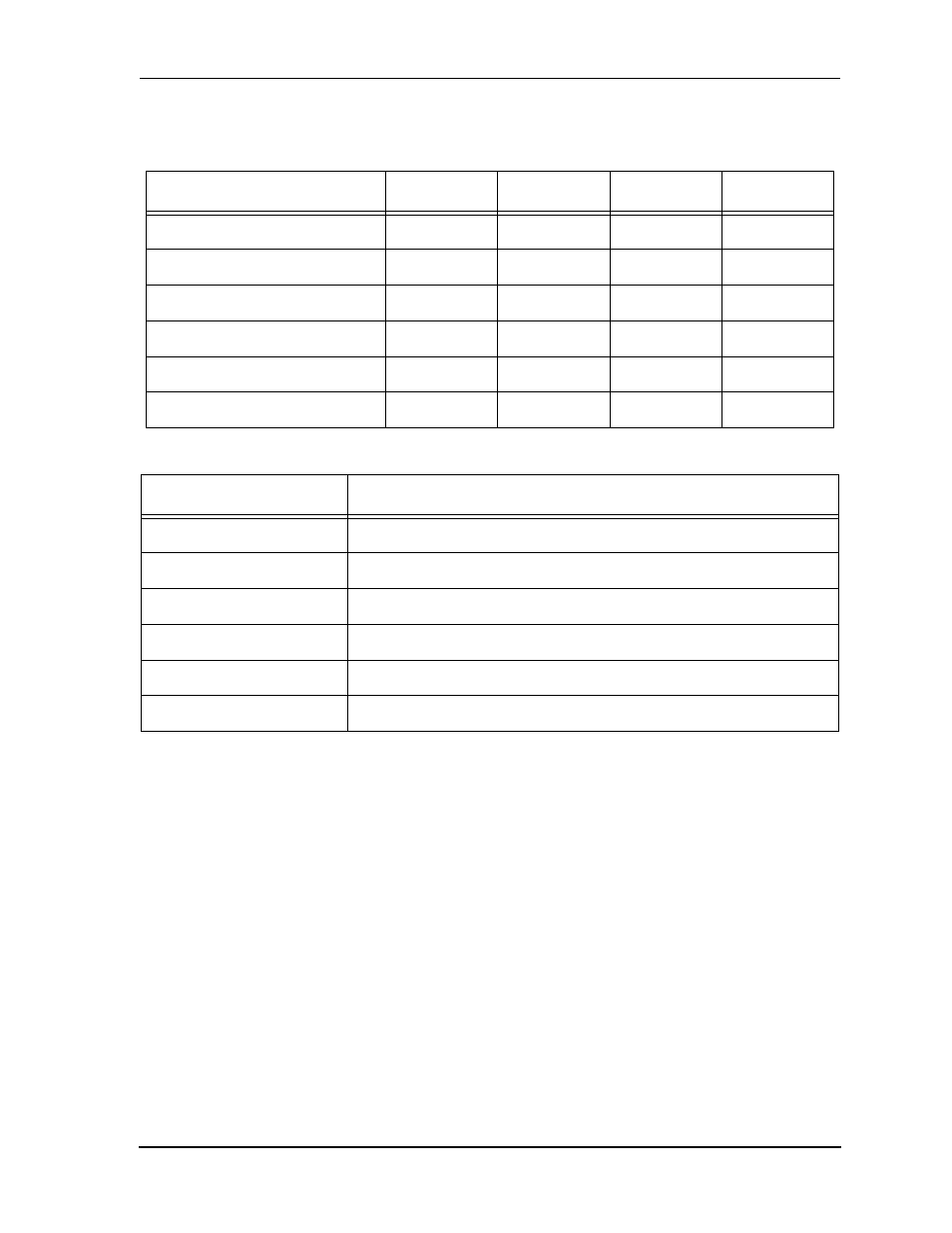

Table 6-1

SAI Interrupt Vector Locations

Interrupt

TXIL = 0

TXIL = 1

RXIL = 0

RXIL = 1

Left Channel Transmit

P: $0010

P: $0040

—

—

Right Channel Transmit

P: $0012

P: $0042

—

—

Transmit Exception

P: $0014

P: $0044

—

—

Left Channel Receive

—

—

P: $0016

P: $0046

Right Channel Receive

—

—

P: $0018

P: $0048

Receive Exception

—

—

P: $001A

P: $004A

Table 6-2

SAI Internal Interrupt Priorities

Priority

Interrupt

Highest

SAI Receive

SAI Transmit

SAI Left Channel Receive

SAI Left Channel Transmit

SAI Right Channel Receive

Lowest

SAI Right Channel Transmit