Motorola DSP56012 User Manual

Page 71

Memory, Operating Modes, and Interrupts

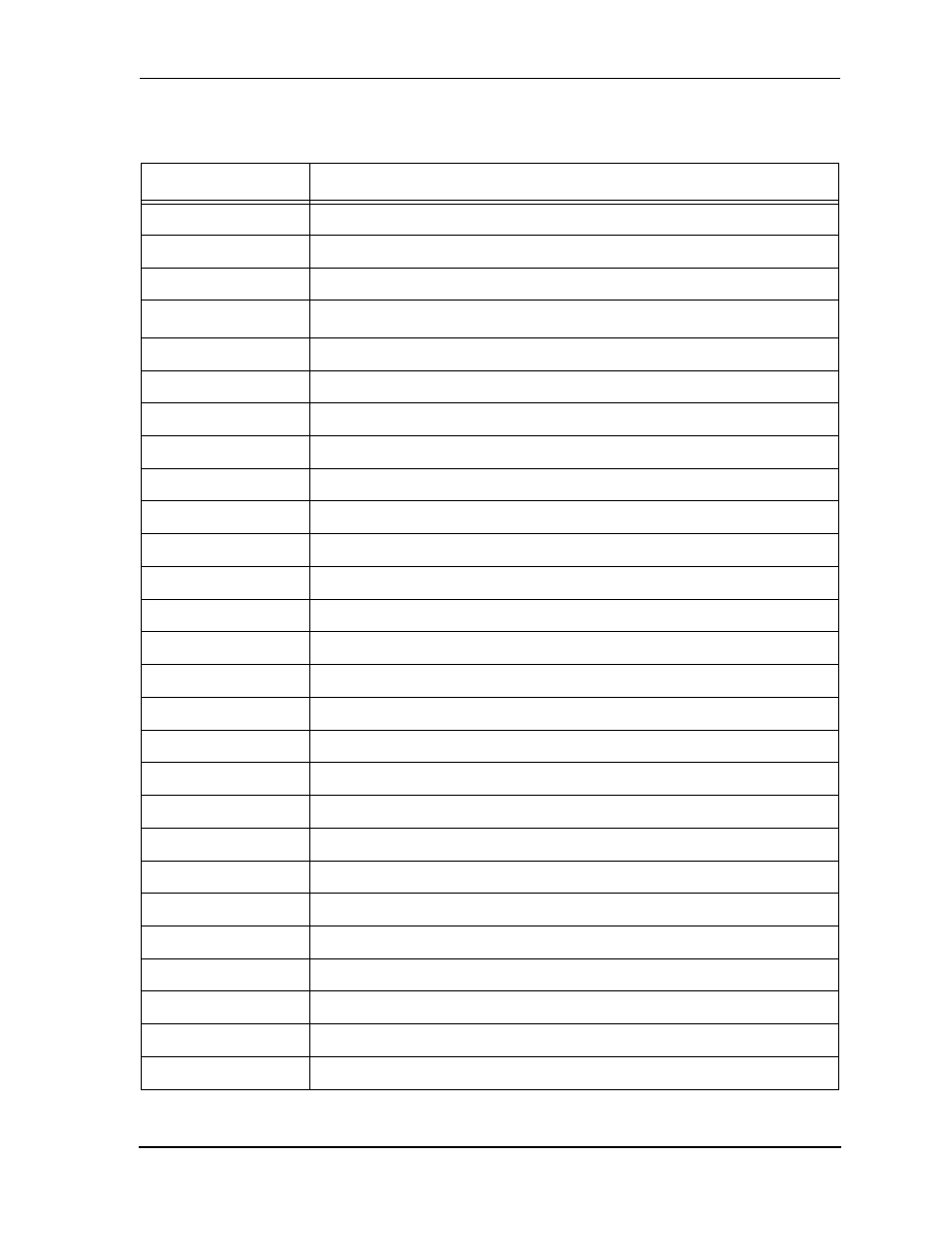

DSP56012 Data and Program Memory Maps

MOTOROLA

DSP56012 User’s Manual

3-11

X: $FFF5

Reserved

X: $FFF4

Reserved

X: $FFF3

SHI Receive FIFO/Transmit Register (HRX/HTX)

X: $FFF2

SHI I

2

C Slave Address Register (HSAR)

X: $FFF1

SHI Host Control/Status Register (HCSR)

X: $FFF0

SHI Host Clock Control Register (HCKR)

X: $FFEF

Reserved

X: $FFEE

Port B Data Register (PBD)

X: $FFED

Port B Data Direction Register (PBDDR)

X: $FFEC

Port B Control Register (PBC)

X: $FFEB

Host Receive/Transmit Register (HORX/HOTX)

X: $FFEA

Reserved

X: $FFE9

Host Status Register (HSR)

X: $FFE8

Host Control Register (HCR)

X: $FFE7

SAI TX2 Data Register (TX2)

X: $FFE6

SAI TX1 Data Register (TX1)

X: $FFE5

SAI TX0 Data Register (TX0)

X: $FFE4

SAI TX Control/Status Register (TCS)

X: $FFE3

SAI RX1 Data Register (RX1)

X: $FFE2

SAI RX0 Data Register (RX0)

X: $FFE1

SAI RX Control/Status Register (RCS)

X: $FFE0

SAI Baud Rate Control Register (BRC)

X: $FFDF

DAX Status Register (XSTR)

X: $FFDE

DAX Control Register (XCTR)

X: $FFDD

Reserved

X:$FFDC

DAX Transmit Data Registers (XADRA and XADRB)

X:$FFDB–FFC0

Reserved

Table 3-2

Internal I/O Memory Map (Continued)

Location

Register