Figure37 pll configuration, 8 operation on hardware reset, Operation on hardware reset -20 – Motorola DSP56012 User Manual

Page 80: Figure 3-7, Pll configuration -20, Operation on hardware reset -19

3-20

DSP56012 User’s Manual

MOTOROLA

Memory, Operating Modes, and Interrupts

Operation on Hardware Reset

3.8

OPERATION ON HARDWARE RESET

The processor enters the Reset processing state when the external RESET pin is

asserted (hardware reset occurs). The Reset state:

• resets internal peripheral devices and initializes their control registers as

described in the peripheral sections,

• sets the modifier registers to $FFFF,

• clears the Interrupt Priority Register,

• clears the Stack Pointer,

• clears the Scaling mode, Trace mode, Loop Flag, Double Precision Multiply

mode and condition code bits, and sets the interrupt mask bits of the Status

Register (SR), and

• clears the Stop Delay (SD) bit and the Program RAM Enable (PEA and PEB)

bits in the OMR.

The DSP remains in the Reset state until the RESET pin is deasserted. When the

processor leaves the Reset state it:

• loads the chip operating mode bits of the OMR from the external mode select

pins (MODC, MODB, MODA), and

• begins program execution of the bootstrap ROM starting at address $0000.

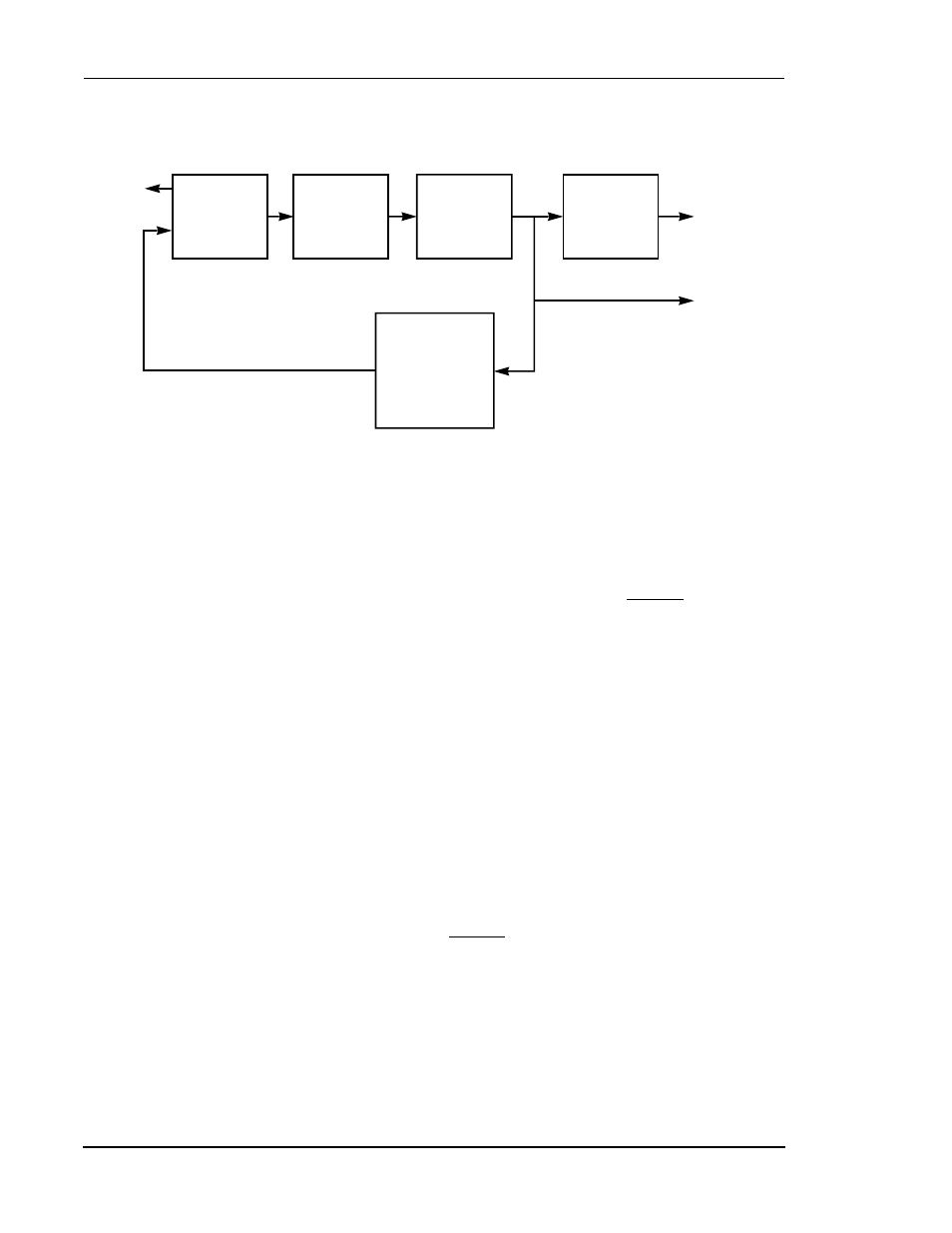

Figure 3-7 PLL Configuration

Divider Out

EXTAL

VCO Out

MF[11:0]

DF[3:0]

Phase

Detector

(PD)

Charge

Pump

Loop

Filter

Voltage

Controlled

Oscillator

(VCO)

Low

Power

Divider

2

0

to 2

15

Multiplication

Factor

1 to 4096

Frequency

Multiplier

AA0293k