6 host interface (hi), Table26 host interface (continued), Host interface (hi) -10 – Motorola DSP56012 User Manual

Page 50: Table 2-6, Host interface -10

2-10

DSP56012 User’s Manual

MOTOROLA

Signal Descriptions

Host Interface (HI)

2.6

HOST INTERFACE (HI)

The HI provides a fast parallel data to 8-bit port, which may be connected directly

to the host bus. The HI supports a variety of standard buses, and can be directly

connected to a number of industry standard microcomputers, microprocessors,

DSPs, and DMA hardware.

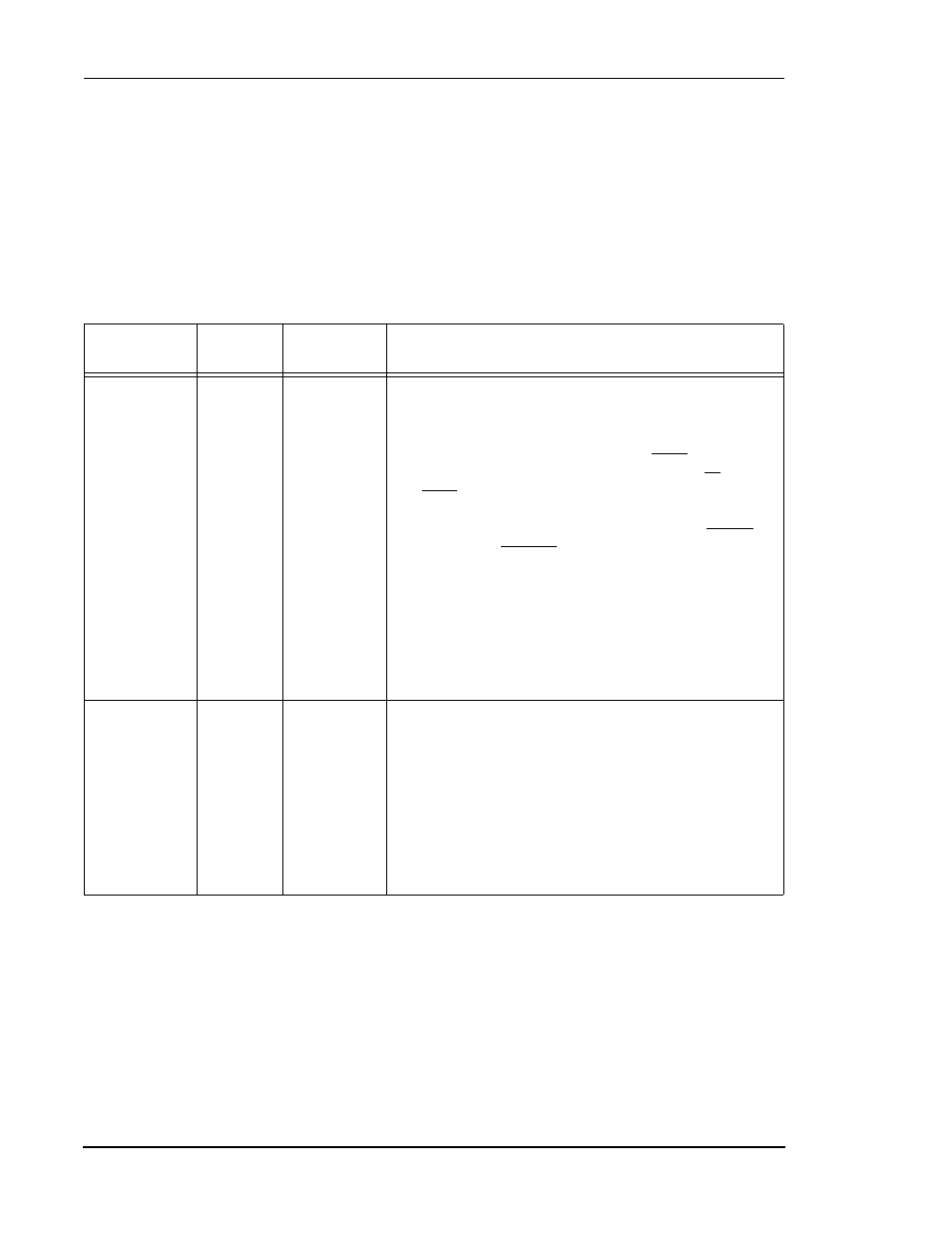

Table 2-6

Host Interface

Signal Name

Type

State During

Reset

Signal Description

H0–H7

PB0–PB7

Input/

Output

Input

Host Data Bus (H0–H7)

—This data bus transfers data

between the host processor and the DSP56012.

When configured as a Host Interface port, the

H0–H7signals are tri-stated as long as HEN is

deasserted. The signals are inputs unless HR/W is high

and HEN is asserted, in which case H0–H7 become

outputs, allowing the host processor to read the

DSP56012 data. H0–H7 become outputs when HACK is

asserted during HOREQ assertion.

Port B GPIO 0–7 (PB0–PB7)

—These signals are General

Purpose I/O signals (PB0–PB7) when the Host Interface is

not selected.

After reset, the default state for these signals is GPIO

input.

HOA0–HOA2

PB8–PB10

Input

Input/

Output

Input

Host Address 0 – Host Address 2

(HOA0–HOA2)

—These inputs provide the address

selection for each Host Interface register.

Port B GPIO 8–10 (PB8–PB10)

—These signals are

General Purpose I/O signals (PB8–PB10) when the Host

Interface is not selected.

After reset, the default state for these signals is GPIO

input.