1 introduction, Figure41 port b interface, 2 port b configuration – Motorola DSP56012 User Manual

Page 83: Introduction -3, Port b configuration -3, Figure 4-1, Port b interface -3

Parallel Host Interface

Introduction

MOTOROLA

DSP56012 User’s Manual

4-3

4.1

INTRODUCTION

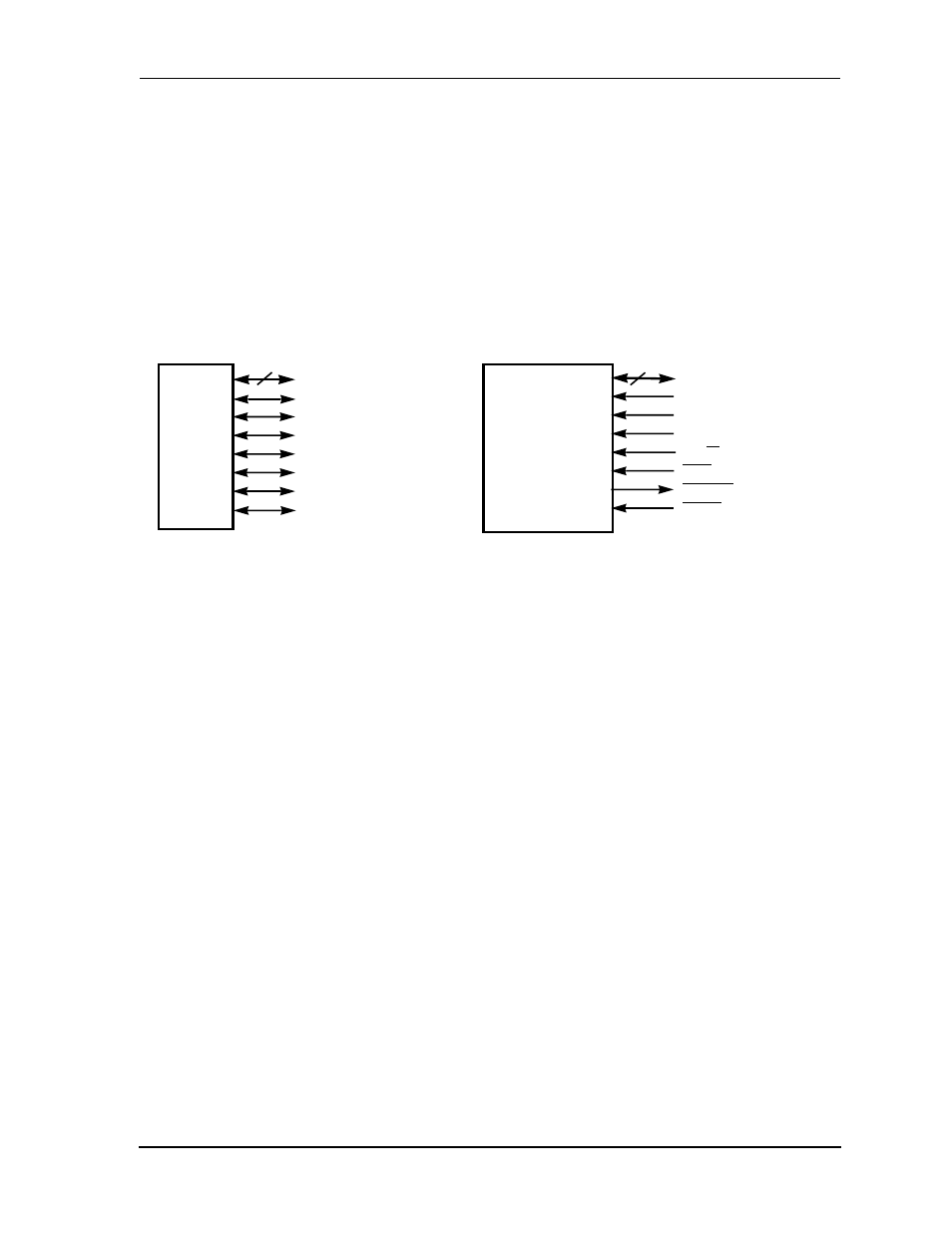

The parallel Host Interface (HI) can serve as an 8-bit, bidirectional parallel port or, as

Port B, a set of General Purpose Input/Output (GPIO) signals (see

). When

configured as the HI, the port provides a convenient connection to another processor.

Port B supports up to fifteen GPIO pins, each pin individually configurable as an

output or an input. This section describes both functions, including examples of how

to configure and use this port.

4.2

PORT B CONFIGURATION

Port B functionality is controlled by three memory-mapped registers (see

on page 4-4) that define the functions associated with fifteen external pins (see

• Port B Control register (PBC)

• Port B Data Direction Register (PBDDR)

• Port B Data register (PBD)

on page 4-6 shows an overview of the Port B control logic.

Note:

Because reset clears both the PBC and PBDDR registers, the default function of

the fifteen specified pins following reset is GPIO input.

Note:

Circuitry connected to the Port B pins may need external pull-ups until the

pins are configured for operation.

Figure 4-1 Port B Interface

Parallel

Host

Interface

Port B

I/0

(15)

PB0–PB7

PB8

PB9

PB10

PB11

PB12

PB13

PB14

H0–H7

HOA0

HOA1

HOA2

HR/W

HEN

HOREQ

HACK

8

8