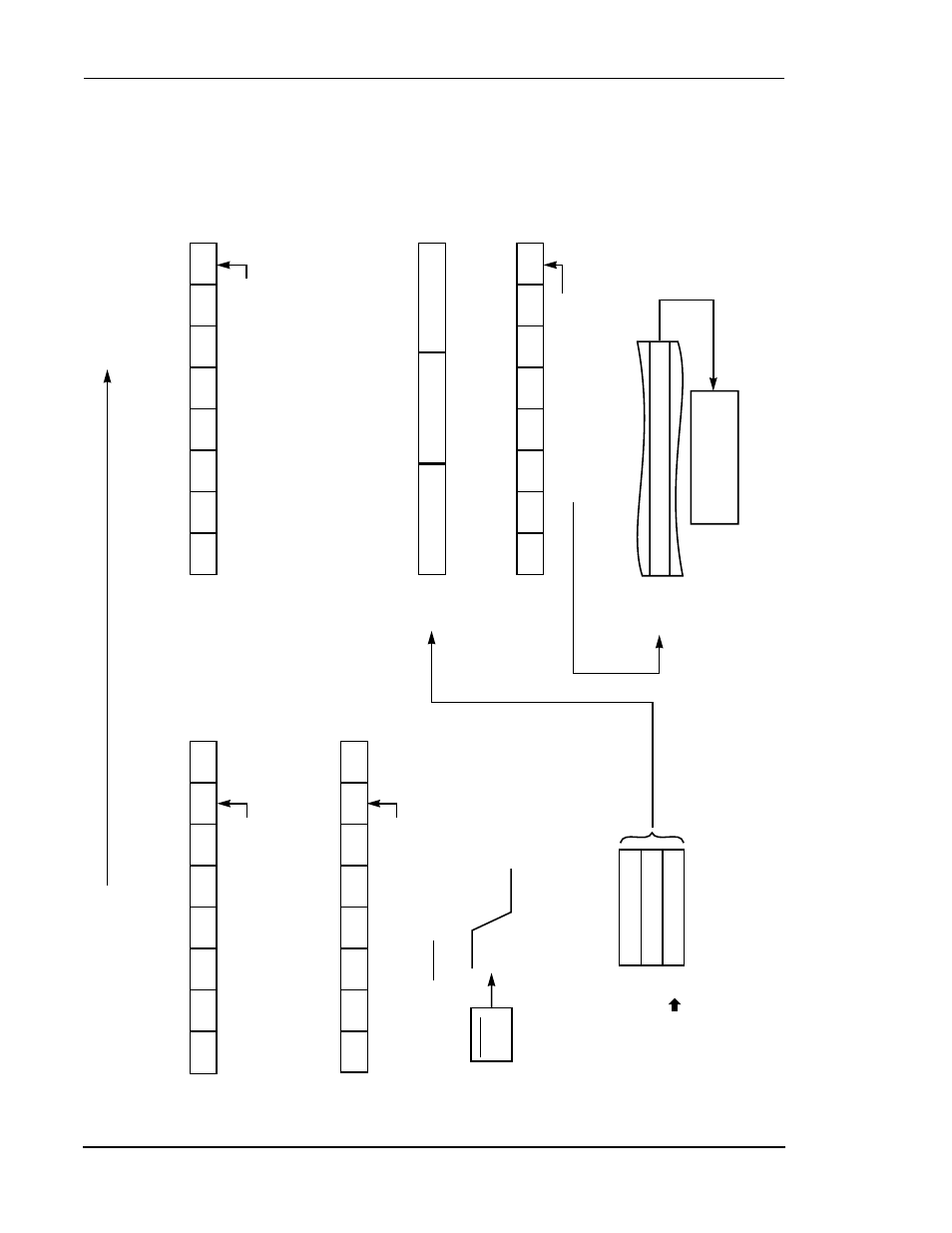

Figure426 data transfer from host to dsp, Figure 4-26, Data transfer from host to dsp -50 – Motorola DSP56012 User Manual

Page 130: Figure 4-26 data transfer from host to dsp, Parallel host interface host interface (hi)

4-50

DSP56012 User’s Manual

MOTOROLA

Parallel Host Interface

Host Interface (HI)

Figure 4-26

Data Transfer from Host to DSP

TRANSFER

$2

INTERRUPT

STATUS

REGISTER (ISR)

$0

VIEW FROM HOST

VIEW FROM DSP56012

1.

WHEN TXDE = 1, TDR IS EMPTY.

X:$FFE9

HOST STATUS

REGISTER (HSR)

X:$FFE8

HOST CONTROL

REGISTER (HCR)

TXDE

TRANSMIT DATA REGISTER EMPTY

INTERRUPT CONTROL

REGISTER (ICR)

2.

HOST can POLL TXDE.

TREQ

TRANSMIT REQUEST ENABLE

3.

IF TREQ = 1, THEN HOREQ

PIN IS ASSERTED TO INTERRUPT HOST.

HOREQ

PIN

4.

HOST WRITES DATA TO TRANSMIT BYTE REGISTERS.

5.

WRITE TO TXL CLEARS TXDE IN ISR.

TRANSMIT BYTE

REGISTERS (TBR)

8.

WHEN TXDE = 0 AND HRDF = 0, THEN TRANSFER OCCURS.

HRDF

HOST RECEIVE DATA FULL

DMA

X:$FFEB

HOST RECEIVE

DATA

REGISTER

(HORX)

9.

THE TRANSFER SETS HRDF FOR THE DSP56012 TO POLL.

HRIE

HOST RECEIVE INTERRUPT ENABLE

P:$0030

HOST RECEIVE DATA VECTOR

FAST INTERRUPT

OR

LONG INTERRUPT

HOREQ

HF3

HF2

1

RXDF

70

0

DMA

6

5

432

1

00

HF1

HF0

HTDE

0

70

0

0

6

5

432

1

HCP

INIT

HF1

HF0

1

RREQ

70

0

0

6

5

432

1

0

HM1

HM0

HIGH BYTE

23

0

MIDDLE BYTE

LOW BYTE

LAST WRITE

$5

$6

$7

TXH

TXM

TXL

10.

IF HRDF = 1 AND INTERRUPTS ARE ENABLED, THEN

interrupt PROCESSING BEGINS.

0

HF3

HF2

HTIE

1

70

0

0

6

5

432

1

HCIE

7.

WHEN DSP56012 READS HORX, THEN HRDF = 0.

6.

IF DSP56012 HAS OLD DATA IN HORX, THEN HRDF = 1.

70

AA0334