Figure436 dma transfer and hi interrupts, 1 host to dsp—internal processing, Host to dsp—internal processing -61 – Motorola DSP56012 User Manual

Page 141: Figure 4-36, Dma transfer and hi interrupts -61, Parallel host interface host interface (hi)

Parallel Host Interface

Host Interface (HI)

MOTOROLA

DSP56012 User’s Manual

4-61

4.4.8.3.1

Host to DSP—Internal Processing

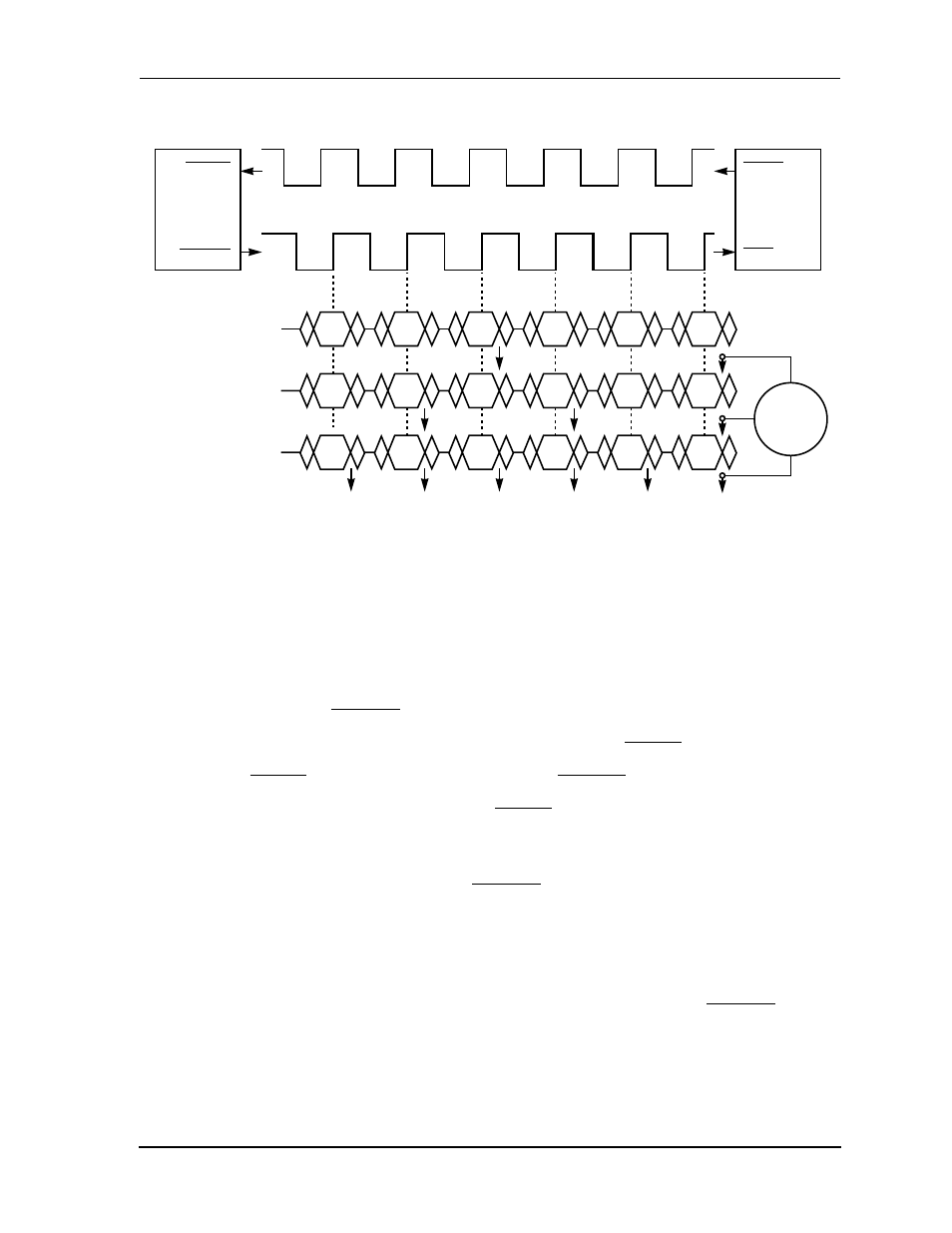

The following procedure outlines the steps that the HI hardware takes to transfer

DMA data from the host data bus to DSP memory (see

1. Host asserts the HOREQ pin when TXDE = 1.

2. DMA controller enables data on H0–H7 and asserts HACK.

3. When HACK is asserted, the host deasserts HOREQ.

4. When the DMA controller deasserts HACK, the data on H0–H7 is latched into

the TXH, TXM, TXL registers.

5. If the byte register written was not TXL (i.e., not $7), the DMA address counter

internal to the HI increments and HOREQ is again asserted. Steps 2–5 are then

repeated.

6. If TXL ($7) was written, TXDE will be cleared and the address counter in the

HI will be loaded with the contents of HM1 and HM0. When TXDE = 0, the

contents of TXH:TXM:TXL are transferred to HORX (provided that

HRDF = 0). After the transfer to HORX, TXDE will be set, and HOREQ will be

asserted to start the transfer of another word from external memory to the HI.

Figure 4-36 DMA Transfer and HI Interrupts

XFEREQ

XFERACK

DMA

CONTROLLER

HOREQ

HACK

DSP56012

24-BIT TRANSFER

(INTERNAL COUNTER)

16-BIT TRANSFER

(INTERNAL COUNTER)

8-BIT TRANSFER

(INTERNAL COUNTER)

H

(01)

M

(10)

M

(10)

M

(10)

M

(10)

M

(10)

H

(01)

L

(11)

L

(11)

L

(11)

L

(11)

L

(11)

L

(11)

L

(11)

L

(11)

L

(11)

L

(11)

L

(11)

HOST

RECEIVE

INTERRUPT

FAST INTERRUPT ROUTINE

P:$0030 MOVE X:$FFE8, A READ HORX

P:$0031 MOVE A, Y:(R7)+; AND PUT INTO Y MEMORY

AA0342.11