1 parallel host interface (hi), 2 serial host interface (shi), Parallel host interface (hi) -18 – Motorola DSP56012 User Manual

Page 38: Serial host interface (shi) -18

1-18

DSP56012 User’s Manual

MOTOROLA

Overview

DSP56012 Architectural Overview

1.3.4.1

Parallel Host Interface (HI)

The parallel Host Interface (HI) is a byte-wide, full-duplex, double-buffered, parallel

port that can be connected directly to the data bus of a host processor. The host

processor can be any of a number of industry-standard microcomputers or

microprocessors, another DSP, or DMA hardware, because this interface looks like

static memory to the host processor. The HI is asynchronous and consists of two sets

of registers—one set accessible only to the host processor and a second set accessible

only to the DSP CPU (see

Section 4, Parallel Host Interface

).

1.3.4.2

Serial Host Interface (SHI)

The Serial Host Interface (SHI) provides a serial path for communication and

program/coefficient data transfers between the DSP and an external host processor

or other serial peripheral devices. This interface can connect directly to one of two

well-known and widely-used synchronous serial buses: the Serial Peripheral

Interface (SPI) bus defined by Motorola and the Inter Integrated-circuit Control (I

2

C)

bus defined by Philips. The SHI handles both SPI and I

2

C bus protocols as required

from a slave or a single-master device. In order to minimize DSP overhead, the SHI

supports single-, double-, and triple-byte data transfers. An optimal ten-word receive

FIFO register reduces the DSP overhead for data reception (see

Section 5, Serial

Host Interface

).

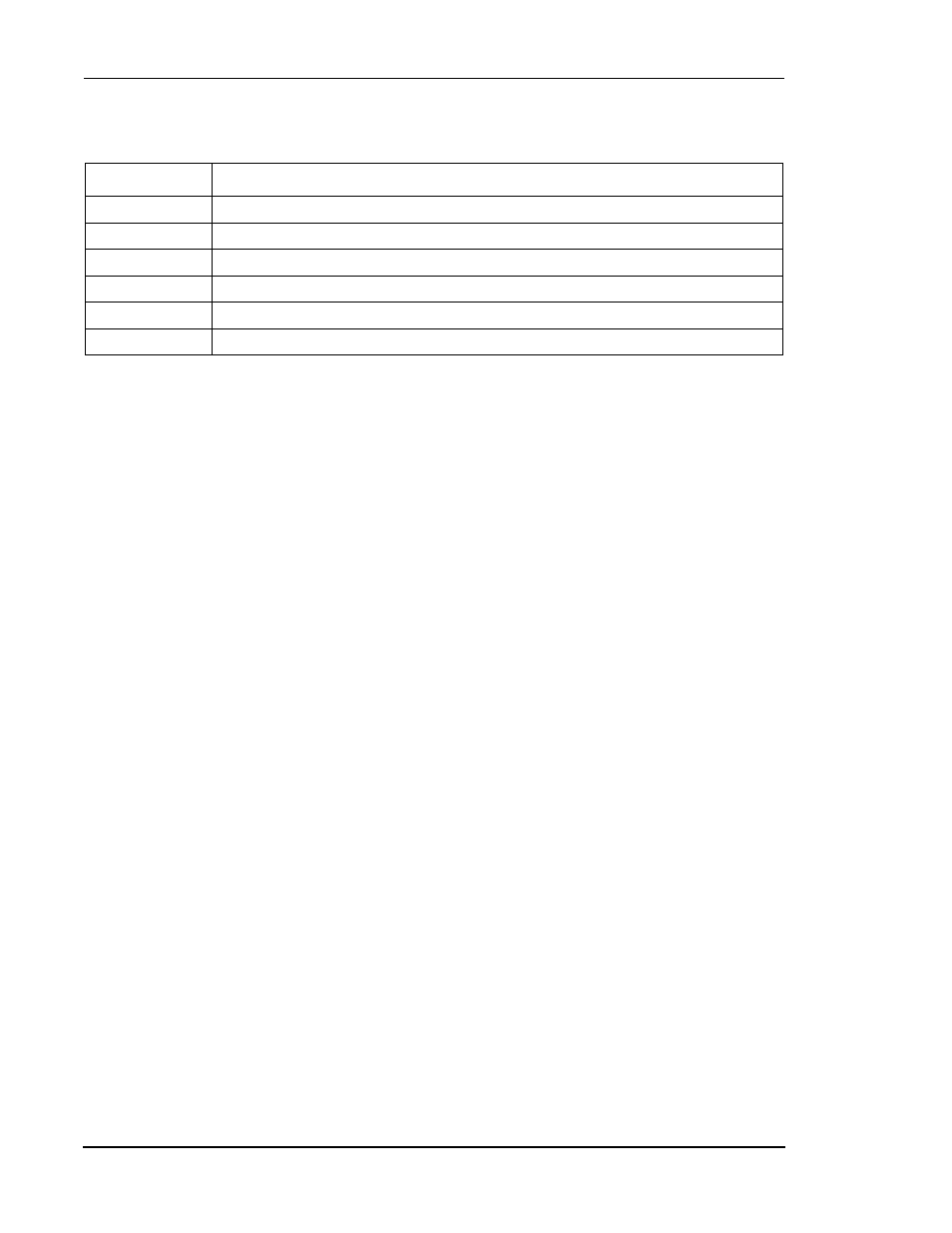

X:$FFDE

DAX Control Register (XCTR)

X:$FFDD

Reserved

X:$FFDC

DAX Transmit Data Registers (XADRA/XADRB)

X:$FFDB

Reserved

:

:

X:$FFC0

Reserved

Table 1-5

On-chip Peripheral Memory Map (Continued)

Address

Register