11 tcs transmitter interrupt enable (txie)—bit 11, Tcs transmitter interrupt enable (txie)—bit 11 -21, Figure 6-14 – Motorola DSP56012 User Manual

Page 199

Serial Audio Interface

Serial Audio Interface Programming Model

MOTOROLA

DSP56012 User’s Manual

6-21

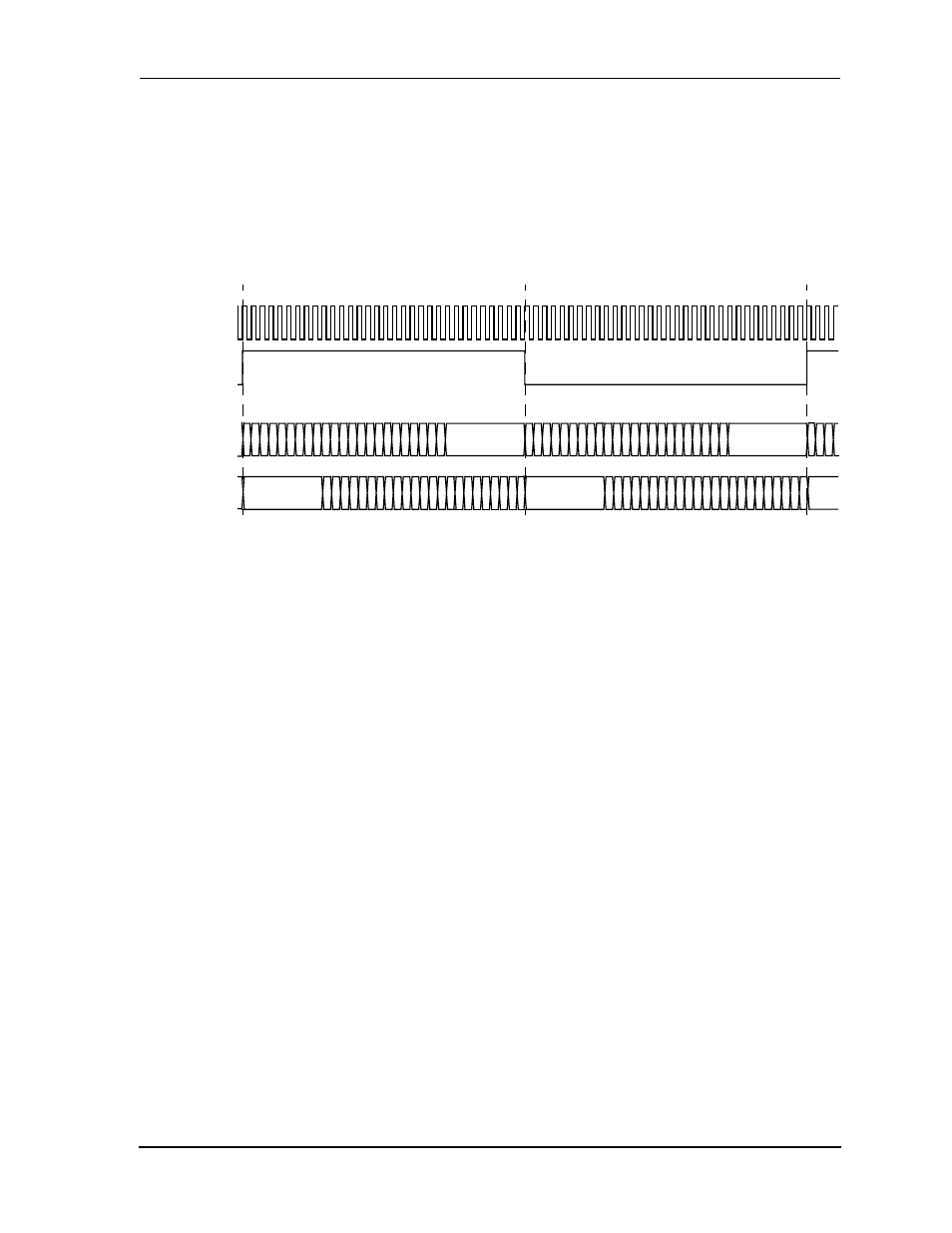

register, the last bit is transmitted eight times. When TDWE is set, the first bit is

transmitted 8 times and then the 24-bit data word from the transmit data register is

transmitted. The TDWE bit is ignored if TWL[1:0] are set for a word length other than

32 bits (see Figure 6-14). The TDWE bit is cleared during hardware reset and

software reset.

6.3.4.11

TCS Transmitter Interrupt Enable (TXIE)—Bit 11

When the read/write Transmitter Interrupt Enable (TXIE) control bit is set,

transmitter interrupts for both left and right data words are enabled, and the DSP is

interrupted if either the TLDE or TRDE status bit is set. When TXIE is cleared,

transmitter interrupts are disabled. However, the TLDE and TRDE bits still signal the

transmit data register empty conditions. Clearing TXIE will mask a pending

transmitter interrupt only after a one-instruction-cycle delay. If TXIE is cleared in a

long interrupt service routine, it is recommended that at least one other instruction

should be inserted between the instruction that clears TXIE and the RTI instruction at

the end of the interrupt service routine.

There are three different transmit data interrupts that have separate interrupt

vectors:

1. Left Channel Transmit interrupt is generated when TXIE = 1, TLDE = 1, and

TRDE = 0. The transmit data registers should be loaded with the left data

words.

2. Right Channel Transmit interrupt is generated when TXIE = 1, TLDE = 0, and

TRDE = 1. The transmit data registers should be loaded with the right data

words.

3. Transmit interrupt with exception (underrun) is generated when TXIE = 1,

TLDE = 1, and TRDE = 1. This means that old data is being retransmitted.

Figure 6-14 Transmitter Data Word Expansion (TDWE) Programming

SDI

WST

SDO

1 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32

SCKT

Left

Right

TDWE = 0

TDWE = 1

1 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32

AA0440k