2 rcs receiver 1 enable (r1en)—bit 1, 3 rcs reserved bit—bits 13 and 2, 4 rcs receiver master (rmst)—bit 3 – Motorola DSP56012 User Manual

Page 189: Table63 receiver word length control, Rcs receiver 1 enable (r1en)—bit 1 -11, Rcs reserved bit—bits 13 and 2 -11, Rcs receiver master (rmst)—bit 3 -11, Table 6-3, Receiver word length control -11

Serial Audio Interface

Serial Audio Interface Programming Model

MOTOROLA

DSP56012 User’s Manual

6-11

which is equivalent to the individual reset state. The R0EN bit is cleared during

hardware reset and software reset.

6.3.2.2

RCS Receiver 1 Enable (R1EN)—Bit 1

The read/write Receiver 1 Enable (R1EN) control bit enables the operation of SAI

Receiver 1. When R1EN is set, Receiver 1 is enabled. When R1EN is cleared, Receiver

1 is disabled. If both R0EN and R1EN are cleared, the receiver section is disabled,

which is equivalent to the individual reset state. The R1EN bit is cleared during

hardware reset and software reset.

6.3.2.3

RCS Reserved Bit—Bits 13 and 2

Bits 13 and 2 in the RCS are reserved and unused. They read as 0s and should be

written with 0s for future compatibility.

6.3.2.4

RCS Receiver Master (RMST)—Bit 3

The read/write control bit Receiver Master (RMST) switches the operation of the

receiver section between Master and Slave modes. When RMST is set, the SAI

receiver section is configured as a master. In the Master mode the receiver drives the

SCKR and WSR pins. When RMST is cleared, the SAI receiver section is configured as

a slave. In the Slave mode, the SCKR and WSR pins are driven from an external

source. The RMST bit is cleared during hardware reset and software reset.

6.3.2.5

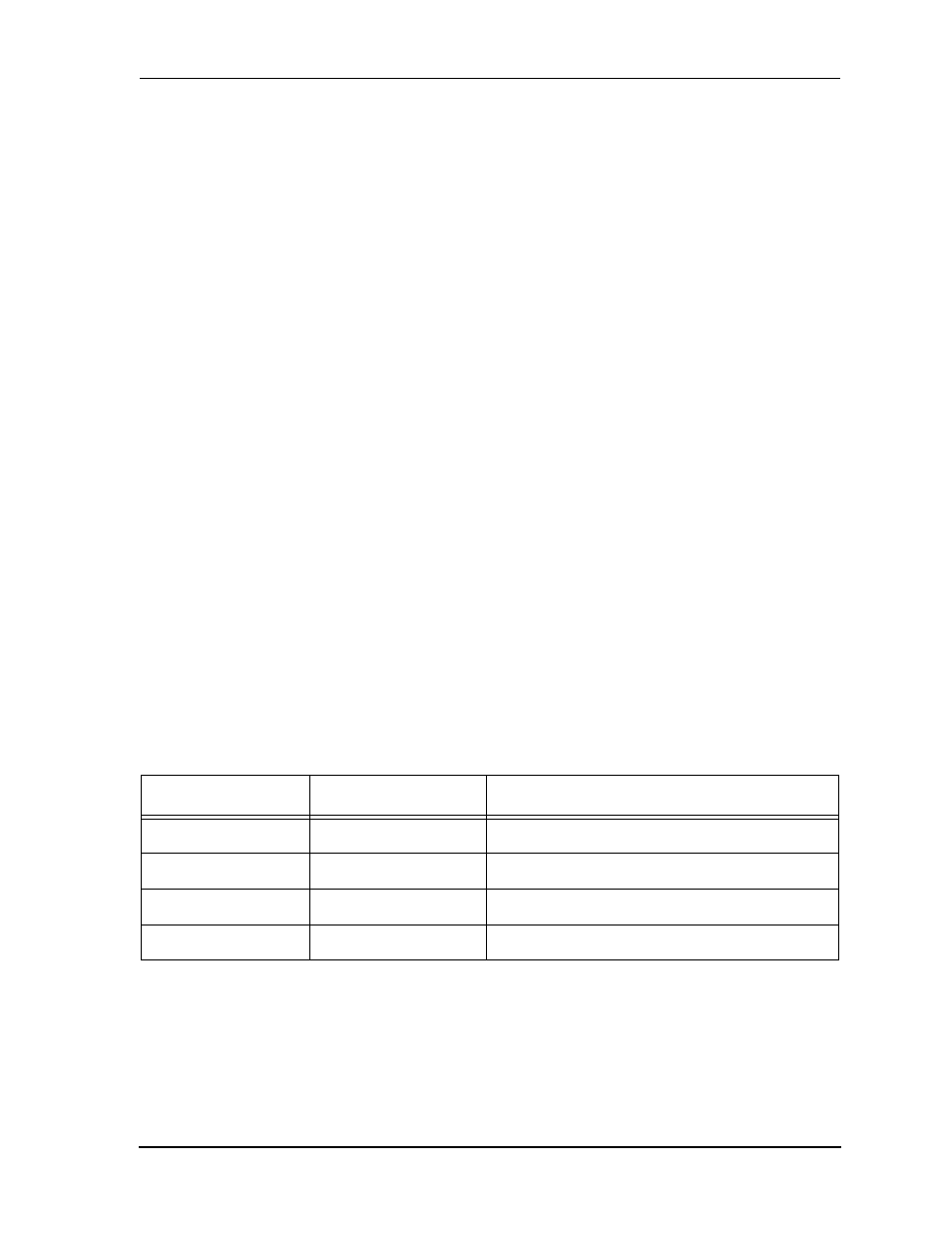

RCS Receiver Word Length Control (RWL[1:0])—Bits 4 and 5

The read/write Receiver Word Length (RWL[1:0]) control bits are used to select the

length of the data words received by the SAI. The data word length is defined by the

number of serial clock cycles between two edges of the word select signal. Word

lengths of 16, 24, or 32 bits may be selected, as shown in Table 6-3.

The receive data registers are always loaded with 24 bits when a new data word

arrives. If the 16-bit word length is selected, the received 16-bit data word will be

placed in the 16 Most Significant Bits of the receive data register, independent of the

Receiver data shift Direction bit (RDIR, see below), while the 8 Least Significant Bits

of the receive data register are cleared. If a 32-bit word length is selected, 8 bits are

Table 6-3

Receiver Word Length Control

RWL1

RWL0

Number of Bits/Word

0

0

16

0

1

24

1

0

32

1

1

Reserved