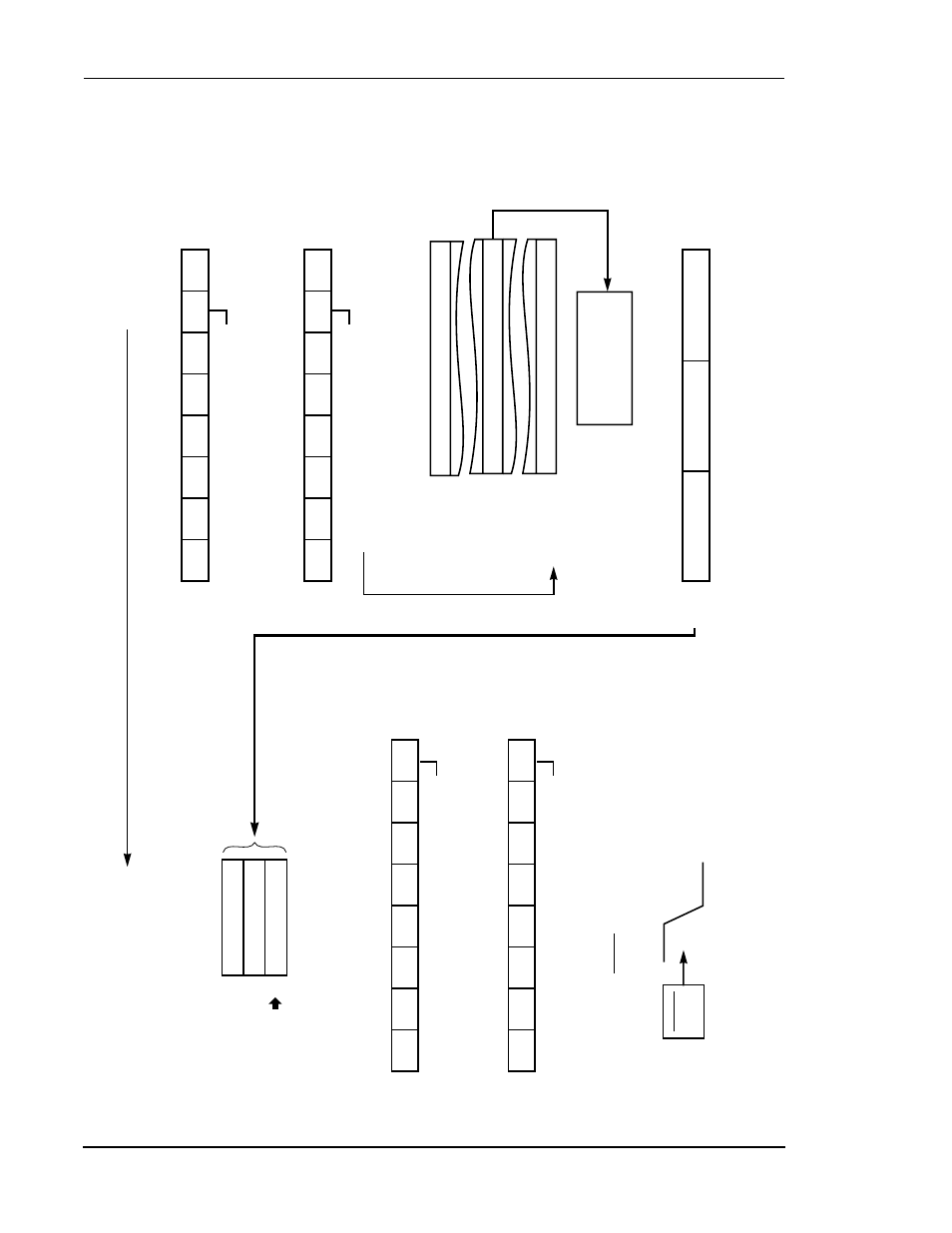

Figure433 data transfer from dsp to host, Figure 4-33, Data transfer from dsp to host -58 – Motorola DSP56012 User Manual

Page 138: Figure 4-33 data transfer from dsp to host, Parallel host interface host interface (hi)

4-58

DSP56012 User’s Manual

MOTOROLA

Parallel Host Interface

Host Interface (HI)

Figure 4-33

Data Transfer from DSP to Host

VIEW FR

OM HOST

X:$FFE8

HOST CONTR

OL

REGISTER (HCR)

1.

WHEN HTDE = 1,

THEN HO

TX IS EMPTY

.

2.

DSP56012 can POLL HTDE.

7.

THE

TRANSFER SETS RXDF FOR

THE HOST

T

O

POLL.

HTDE

HOST

TRANSMIT D

A

T

A

EMPTY

HTIE

HOST

TRANSMIT INTERR

UPT ENABLE

P:$007E

A

V

AILABLE FOR HOST COMMAND

F

AST INTERR

UPT

OR

LONG INTERR

UPT

P:$0000

HOST TRANSMIT

D

A

T

A

VECT

OR

P:$0032

5.

READ OF RXL BY HOST CLEARS RXDF IN ISR.

6.

WHEN RXDF = 0 AND HTDE = 0,

THEN

TRANSFER OCCURS

.

RXH

RXM

RXL

70

$5

$6

LAST READ

$7

RECEIVE BYTE

REGISTERS (RBR)

$2

RXDF

RECEIVE

D

A

T

A

FULL

$0

RREQ

RECEIVE

REQ

UEST ENABLE

8.

IF RREQ = 1,

THEN HOREQ

PIN IS ASSER

TED

T

O

INTERR

UPT HOST

.

HOREQ

PIN

VIEW FR

OM HOST

3.

IF HTIE = 1, AND INTERR

UPTS ARE ENABLED

,

THEN INTERR

UPT

PR

OCESSING BEGINS

.

4.

DSP56012

WRITES D

A

T

A

T

O

HO

TX,

WHICH CLEARS HTDE IN HSR.

X:$FFEB

HOST TRANSMIT

D

ATA

REGISTER (HO

TX)

INTERRUPT

STATUS

REGISTER (ISR)

HOREQ

HF3

HF2

TXDE

1

70

0

DMA

6

5

432

1

TRDY

$X:$FFE9

HOST ST

A

TUS

REGISTER (HSR)

DMA

HF1

HF0

1

HRDF

70

0

0

6

5

432

1

HCP

0

HF3

HF2

1

HRIE

70

0

0

6

5

432

1

HCIE

INIT

HF1

HF0

TREQ

1

70

HM0

HM1

6

5

432

1

0

HIGH BYTE

LOW BYTE

23

0

MIDDLE BYTE

INTERRUPT

CONTROL

REGISTER (ICR)

AA0340K