Figure84 preamble sequence, 10 dax clock multiplexer, Figure85 clock multiplexer diagram – Motorola DSP56012 User Manual

Page 223: Dax clock multiplexer -13, Figure 8-4, Preamble sequence -13, Figure 8-5, Clock multiplexer diagram -13

Digital Audio Transmitter

DAX Internal Architecture

MOTOROLA

DSP56012 User’s Manual

8-13

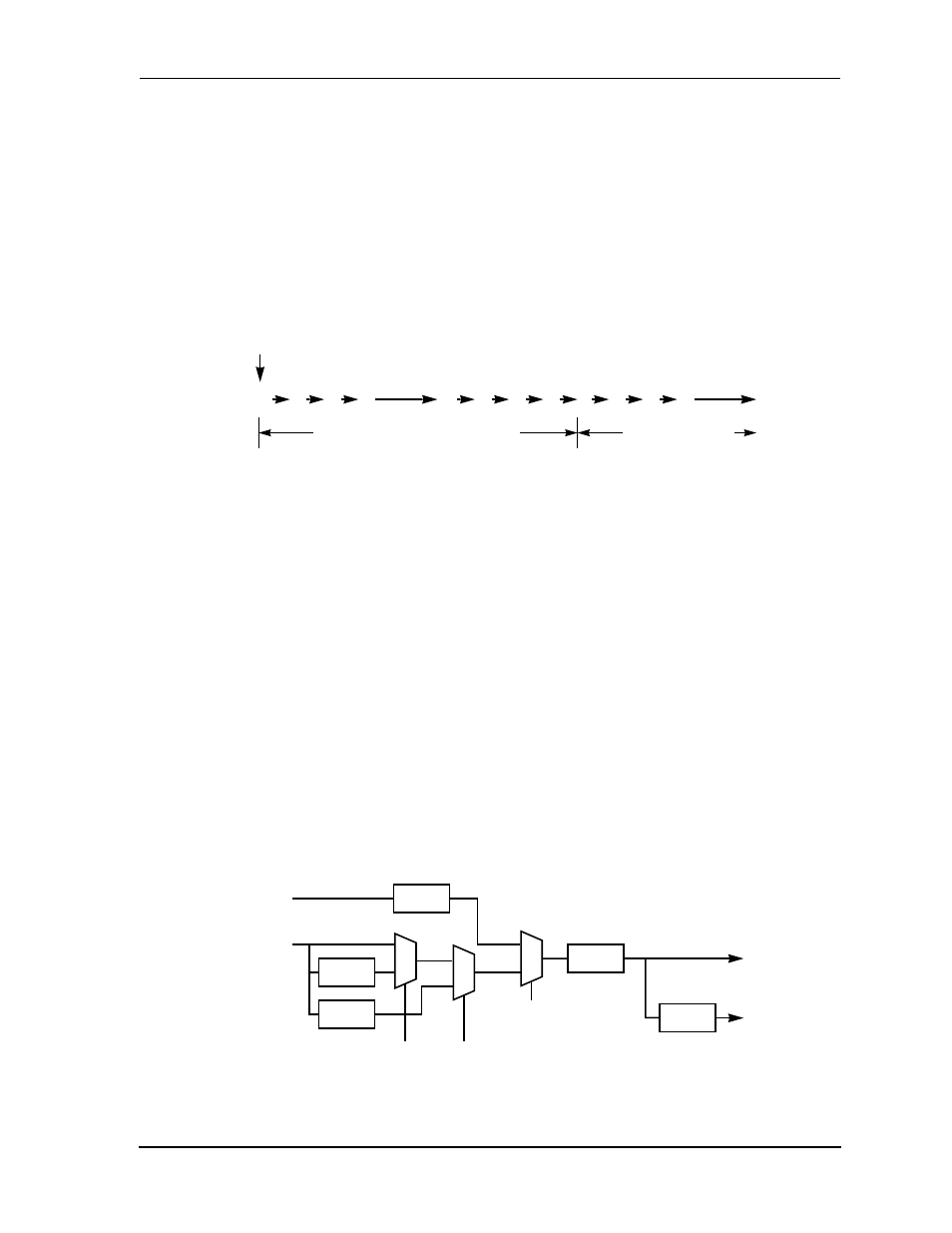

There is no programmable control for the preamble selection. The first sub-frame to

be transmitted (immediately after the DAX is enabled) is the beginning of a block,

and therefore it has a “Z” preamble. This is followed by the second sub-frame, which

has an “Y” preamble. After that, “X” and “Y” preambles are transmitted alternately

until the end of the block transfer (192 frames transmitted). See

illustration of the preamble sequence.

8.5.10

DAX Clock Multiplexer

The DAX clock multiplexer selects one of the clock sources and generates the biphase

clock (128

×

Fs) and shift clock (64

×

Fs). The clock source can be selected from the

following options (see also

Section

• The internal DSP core clock—assumes 1024

×

Fs

• DAX clock input pin(ACI)—512

×

Fs

• DAX clock input pin(ACI)—384

×

Fs

• DAX clock input pin(ACI)—256

×

Fs

shows how each clock is divided to generate the biphase and bit shift

clocks.

Figure 8-4 Preamble sequence

Figure 8-5 Clock Multiplexer Diagram

DAX

Enabled

Here

First Block (384 Sub-frames)

Second Block

Z

Y

X

Y

X

Y

X

Y

Z

Y

X

Y

AA0609k

1/4

2/3

1/2

1/2

1/2

Biphase

Clock

(128

×

Fs)

Bit Shift

Clock

(64

×

Fs)

DSP Core Clock

(1024

×

Fs)

ACI Pin

{256,384,512}

×

Fs

(XCS1 or XCS0)

XCS0

1

0

XCS1

1

0

1

0

MUX

MUX

MUX

AA0610