7 on-chip emulation (once) port, 3 memories, 1 program memory – Motorola DSP56012 User Manual

Page 33: On-chip emulation (once) port -13, Memories -13, Program memory -13, Table 1-3, Interrupt starting addresses and sources -13

Overview

DSP56012 Architectural Overview

MOTOROLA

DSP56012 User’s Manual

1-13

1.3.2.7

On-Chip Emulation (OnCE) Port

The

On-Chip Emulation (OnCE) port provides a sophisticated debugging tool that

allows simple, inexpensive, and speed-independent access to the processor’s internal

registers and peripherals. The OnCE port tells the application programmer the exact

status of most of the on-chip registers, memory locations, and buses, as well as

storing the addresses of the last five instructions that were executed.

1.3.3

Memories

The three independent memory spaces of the DSP56012—X data, Y data, and

program—and their configurations are discussed briefly here. See

Section 3

,

Memory, Operating Modes, and Interrupts

for more detail

.

1.3.3.1

Program Memory

The on-chip program memory is 24-bits wide. Addresses are received from the

Program Control Logic (usually the Program Counter) over the Program Address

Bus (PAB). Program memory may be written using MOVEM instructions. The

interrupt vectors are located in the bottom 128 locations of program memory.

lists the interrupt vector addresses and indicates the Interrupt Priority

Level (IPL) of each interrupt source. Program RAM has many advantages. It

provides a means to develop code efficiently. Programs can be changed dynamically,

allowing efficient overlaying of DSP software algorithms. In this way the on-chip

Program RAM operates as a fixed cache, thereby minimizing accesses to slower

external memory.

The Bootstrap mode, described in

Appendix A

, provides a convenient, low-cost

method to load the DSP56012 Program RAM through the HI or the SHI (using either

SPI or I

2

C formats) after a power-on reset.

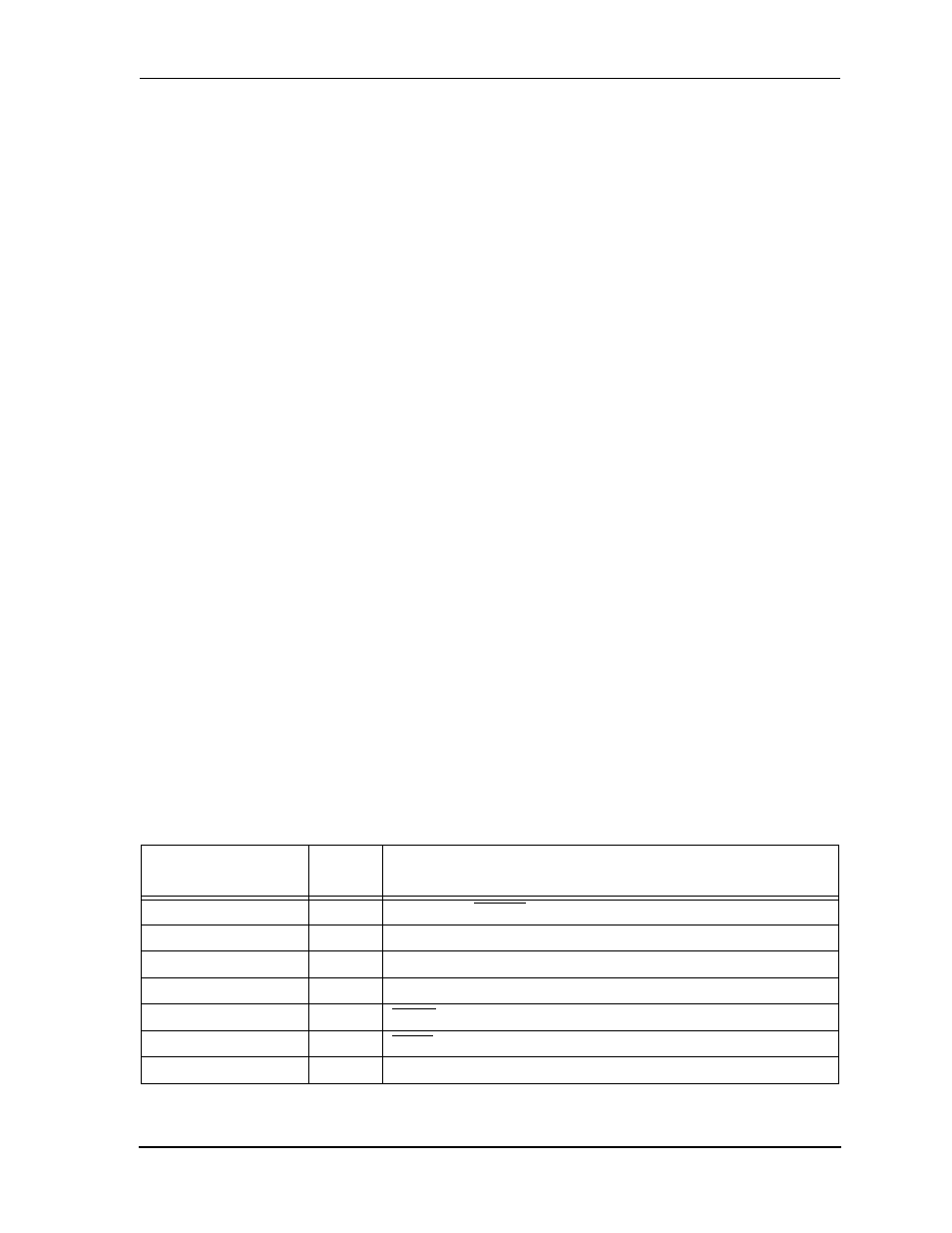

Table 1-3

Interrupt Starting Addresses and Sources

Interrupt

Starting Address

IPL

Interrupt Source

P:$0000

3

Hardware RESET

P:$0002

3

Stack Error

P:$0004

3

Trace

P:$0006

3

SWI

P:$0008

0–2

IRQA

P:$000A

0–2

IRQB

P:$000C

Reserved