Processor side, Programming reference – Motorola DSP56012 User Manual

Page 253

Programming Reference

MOTOROLA

DSP56012 User’s Manual

B-21

Sheet 3 of 5

Application:

Date:

Programmer:

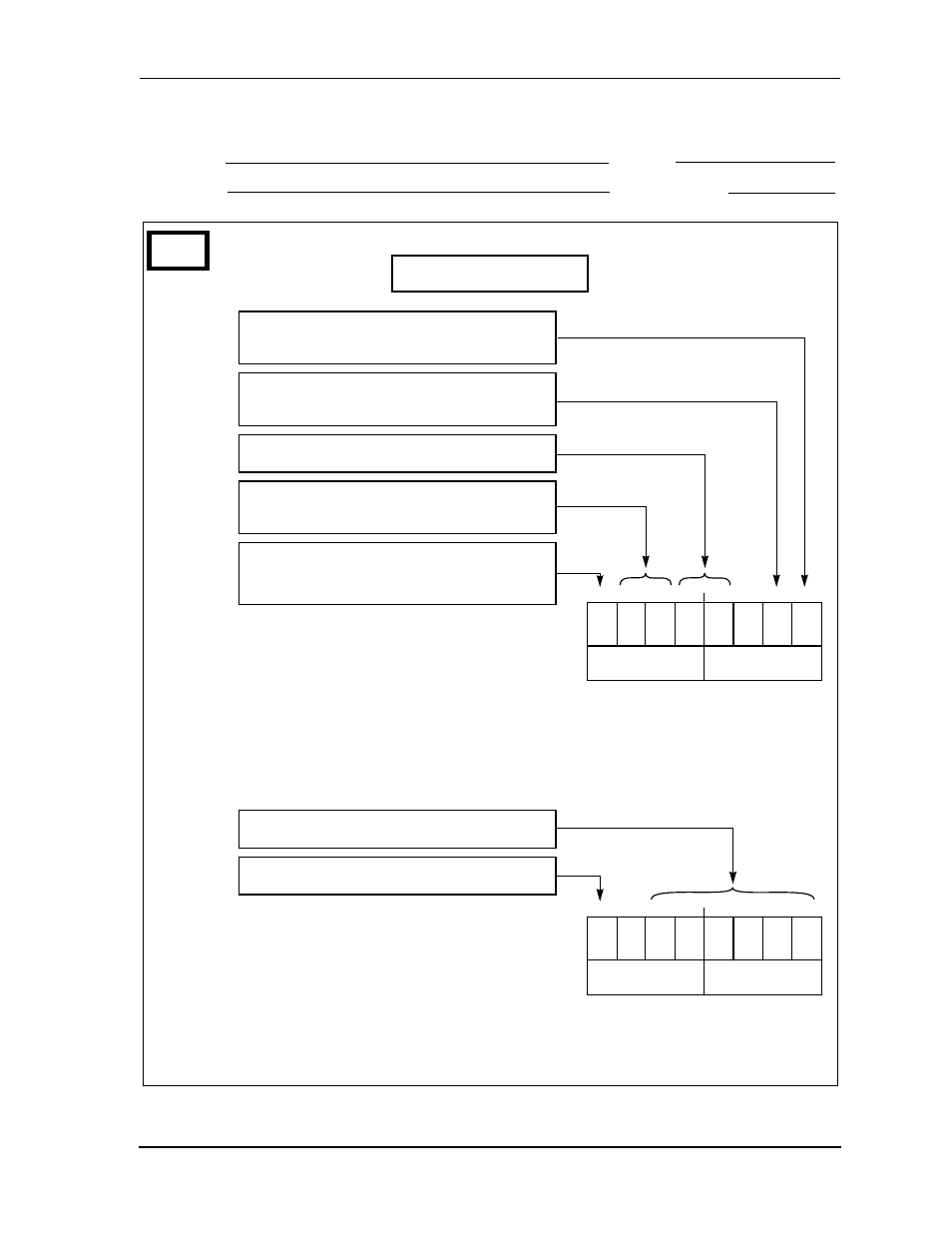

TREQ

HMO

RREQ

HF1

HF0

6

5

4

3

2

1

0

7

* = Reserved, write as 0

*

0

Receive Request Enable (RREQ)

DMA Off: 0 = interrupts disabled/1 = interrupts enabled

Processor Side

INIT

Interrupt Control Register (ICR)

Interrupt Control Register (ICR)

$0 Read/Write

Reset = $00

DMA On: 0 = Host

→

DSP/1 = DSP

→

Host

Transmit Request Enable (TREQ)

DMA Off: 0 = interrupts disabled/1 = interrupts enabled

DMA On: 0 = DSP

→

Host/1 = Host

→

DSP

Host Flags (HF0, HF1)

Write Only

Host Mode Control (HM0, HM1)

00 = DMA off/01 = 24 Bit DMA

10 = 16 Bit DMA/11 = 8 Bit DMA

Initialize (INIT)

0 = no action/1 = initialize DMA

HM1

HV1

HV5

HV0

HV4

HV3

6

5

4

3

2

1

0

7

* = Reserved, write as 0

*

0

HC

Command Vector Register (CVR)

Host Command (HC)

0 = Idle/1 = Interrupt DSP

HV2

Host Vector (HV[5:0])

Executive Interrupt Routine 0-63

Command Vector Register (CVR)

$1 Read/Write

Reset = $17

HI

Write Only