Figureb1 on-chip peripheral memory map, Figure b-1, Programming reference – Motorola DSP56012 User Manual

Page 236

B-4

DSP56012 User’s Manual

MOTOROLA

Programming Reference

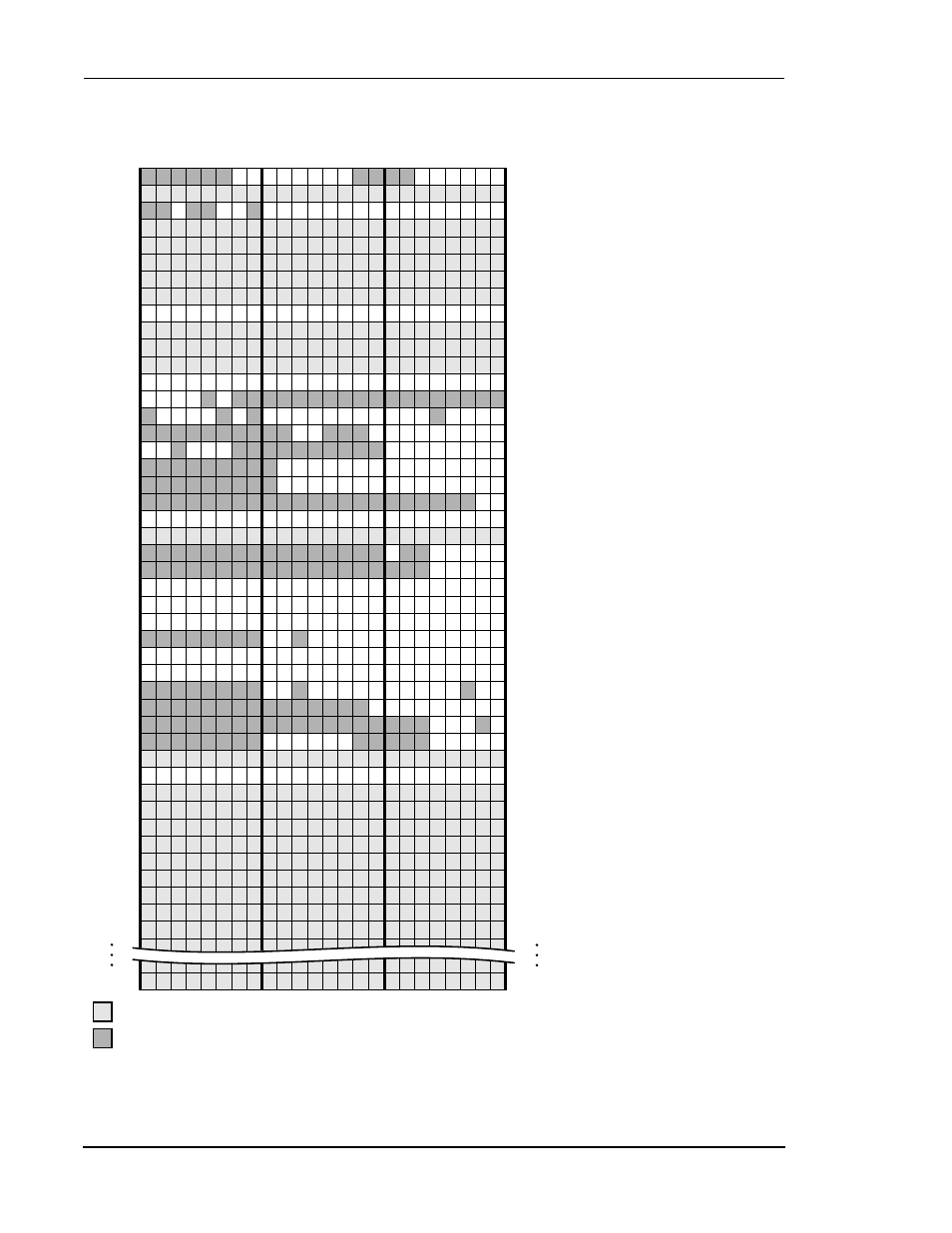

Figure B-1 On-chip Peripheral Memory Map

23

16 15

8 7

0

X:$FFFF

Interrupt Priority Register (IPR)

X:$FFFE

Reserved

X:$FFFD

PLL Control Register (PCTL)

X:$FFFC

Reserved

X:$FFFB

Reserved

X:$FFFA

Reserved

X:$FFF9

Reserved

X:$FFF8

Reserved

X:$FFF7

GPIO Control/Data Register (GPIOR)

X:$FFF6

Reserved

X:$FFF5

Reserved

X:$FFF4

Reserved

X:$FFF3

SHI Receive FIFO/Transmit Register (HRX/HTX)

X:$FFF2

SHI I

2

C Slave Address Register (HSAR)

X:$FFF1

SHI Host Control/Status Register (HCSR)

X:$FFF0

SHI Host Clock Control Register (HCKR)

X:$FFEF

Reserved

X:$FFEE

Port B Data Register (PBD)

X:$FFED

Port B Data Direction Register (PBDDR)

X:$FFEC

Port B Control Register (PBC)

X:$FFEB

HI Receive/Transmit Register (HORX/HOTX)

X:$FFEA

Reserved

X:$FFE9

Host Interface Status Register (HSR)

X:$FFE8

Host Interface Control Register (HCR)

X:$FFE7

SAI TX2 Data Register (TX2)

X:$FFE6

SAI TX1 Data Register (TX1)

X:$FFE5

SAI TX0 Data Register (TX0)

X:$FFE4

SAI TX Control/Status Register (TCS)

X:$FFE3

SAI RX1 Data Register (RX1)

X:$FFE2

SAI RX0 Data Register (RX0)

X:$FFE1

SAI RX Control/Status Register (RCS)

X:$FFE0

SAI Baud Rate Control Register (BRC)

X:$FFDF

DAX Status Register (XSTR)

X:$FFDE

DAX Control Register (XCTR)

X:$FFDD

Reserved

X:$FFDC

DAX Transmit Data Registers (XADRA/XADRB)

X:$FFDB

Reserved

X:$FFDA

Reserved

X:$FFD9

Reserved

X:$FFD8

Reserved

X:$FFD7

Reserved

X:$FFD6

Reserved

X:$FFD5

Reserved

X:$FFD4

Reserved

X:$FFD3

Reserved

X:$FFC0

Reserved

= Unused and reserved; read as a random number; should not be written, to ensure future compatibility

= Unused and reserved; consult the appropriate chapter for information on how to ensure future compatibility