Figure412 hsr and hcr operation, 5 icr hi flag 1 (hf1)—bit 4, 6 icr hi mode control (hm1 and hm0)—bits 5 and 6 – Motorola DSP56012 User Manual

Page 106: Table43 hi mode bit definition, Icr hi flag 1 (hf1)—bit 4 -26, Icr hi mode control (hm1 and hm0)—bits 5 and 64-26, Figure 4-12, Hsr and hcr operation -26, Table 4-3, Hi mode bit definition -26

4-26

DSP56012 User’s Manual

MOTOROLA

Parallel Host Interface

Host Interface (HI)

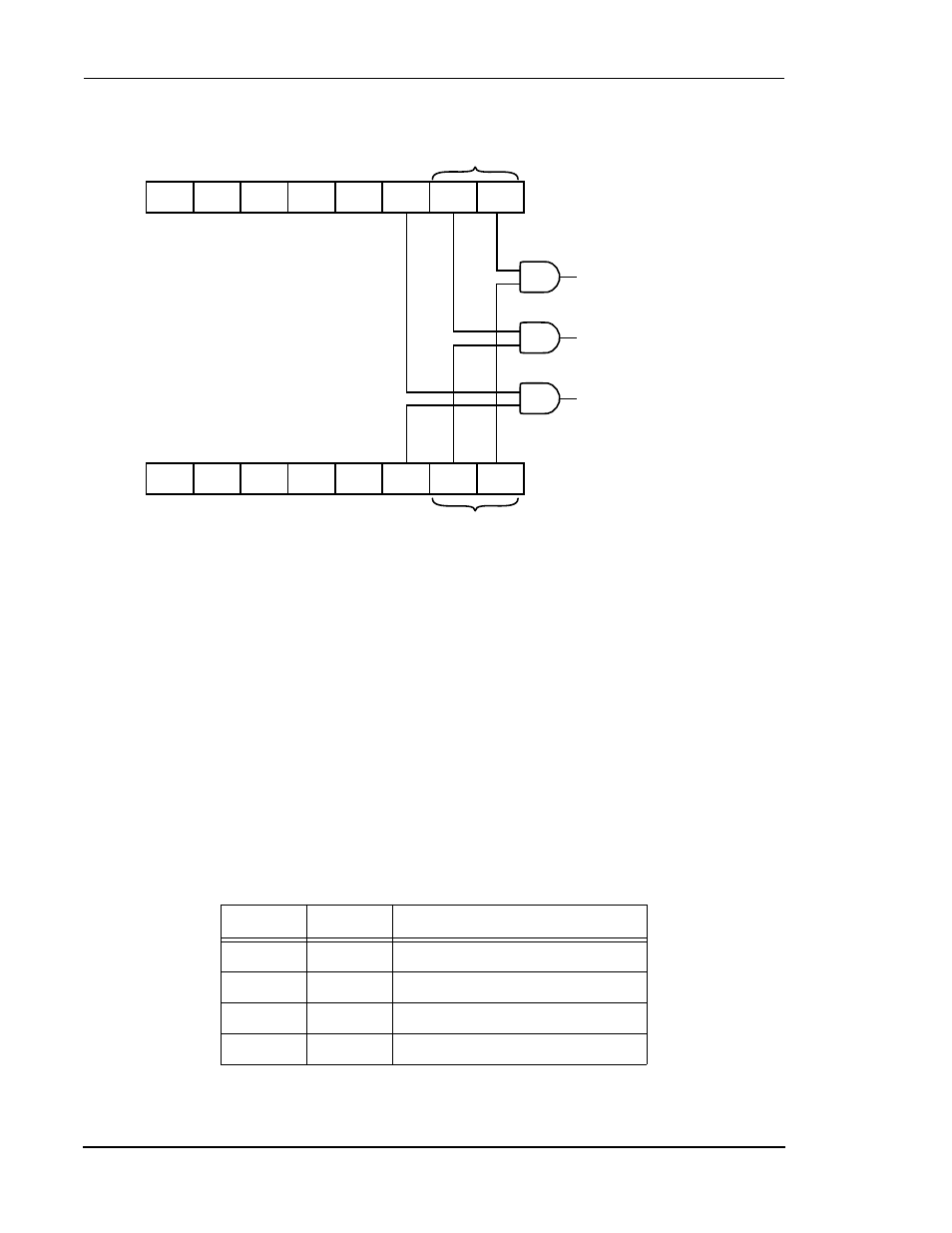

Figure 4-12 HSR and HCR Operation

4.4.5.3.5

ICR HI Flag 1 (HF1)—Bit 4

The HI Flag 1 (HF1) bit is used as a general purpose flag for host-to-DSP

communication. HF1 can be set or cleared by the host processor and cannot be

changed by the DSP.

Note:

Hardware reset, software reset, individual reset, and Stop mode clear HF1.

4.4.5.3.6

ICR HI Mode Control (HM1 and HM0)—Bits 5 and 6

The HI Mode Control 1 (HM1) and HI Mode Control 0 (HM0) bits select the transfer

mode of the HI (see

). HM1 and HM0 enable the DMA mode of operation

or the Interrupt (non-DMA) mode of operation.

Table 4-3

HI Mode Bit Definition

HM1

HM0

Mode

0

0

Interrupt Mode (DMA Off)

0

1

DMA Mode (24-bit)

1

0

DMA Mode (16-bit)

1

1

DMA Mode (8-bit)

Mask

HCR

X:$FFE8

Status

0

HF3

HF2 HCIE HTIE HRIE

7

0

0

0

Receive Data Full

P:$0030

Transmit Data Empty

P:$0032

Host Command

P:(2

×

HV

→

$0000–$007E)

Reset

→

HV = $0017 in CVR

DSP CPU Interrupts

HSR

X:$FFE9

DMA

HF1

HF0

HCP HTDE HRDF

7

0

0

0

AA0317.11