8 rcs receiver clock polarity (rckp)—bit 8, 9 rcs receiver relative timing (rrel)—bit 9, Rcs receiver clock polarity (rckp)—bit 8 -13 – Motorola DSP56012 User Manual

Page 191: Dax signals -4, Figure 6-7, Receiver clock polarity (rckp) programming -13

Serial Audio Interface

Serial Audio Interface Programming Model

MOTOROLA

DSP56012 User’s Manual

6-13

6.3.2.8

RCS Receiver Clock Polarity (RCKP)—Bit 8

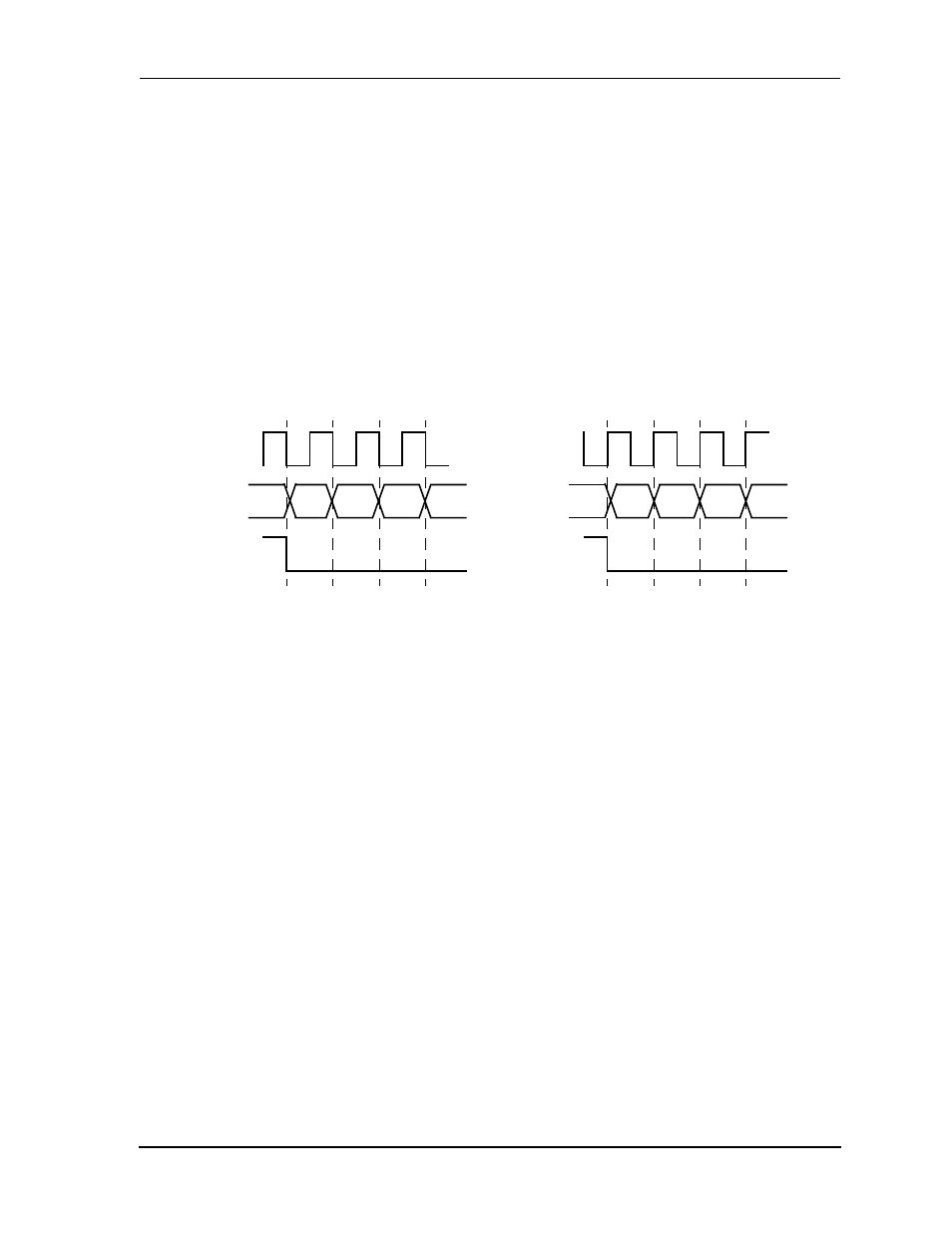

The read/write Receiver Clock Polarity (RCKP) control bit selects the polarity of the

receiver serial clock. When RCKP is cleared, the receiver clock polarity is negative.

When RCKP is set, the receiver clock polarity is positive. Negative polarity means

that the Word Select Receive (WSR) and Serial Data In (SDIx) lines change

synchronously with the negative edge of the clock, and are considered valid during

positive transitions of the clock. Positive polarity means that the WSR and SDIx lines

change synchronously with the positive edge of the clock, and are considered valid

during negative transitions of the clock (see Figure 6-7). The RCKP bit is cleared

during hardware reset and software reset.

6.3.2.9

RCS Receiver Relative Timing (RREL)—Bit 9

The read/write Receiver Relative timing (RREL) control bit selects the relative timing

of the Word Select Receive (WSR) signal as referred to the serial data input lines

(SDIx). When RREL is cleared, the transition of WSR, indicating start of a data word,

occurs together with the first bit of that data word. When RREL is set, the transition

of WSR occurs one serial clock cycle earlier (together with the last bit of the previous

data word), as required by the I

2

S format (see Figure 6-8). The RREL bit is cleared

during hardware reset and software reset.

Figure 6-7 Receiver Clock Polarity (RCKP) Programming

SDI

SCKR

RCKP = 0

SDI

SCKR

RCKP = 1

WSR

WSR

AA0433