Processor side hi, Interrupt status register (isr), Interrupt vector register (ivr) – Motorola DSP56012 User Manual

Page 254: Programming reference

B-22

DSP56012 User’s Manual

MOTOROLA

Programming Reference

Sheet 4 of 5

Application:

Date:

Programmer:

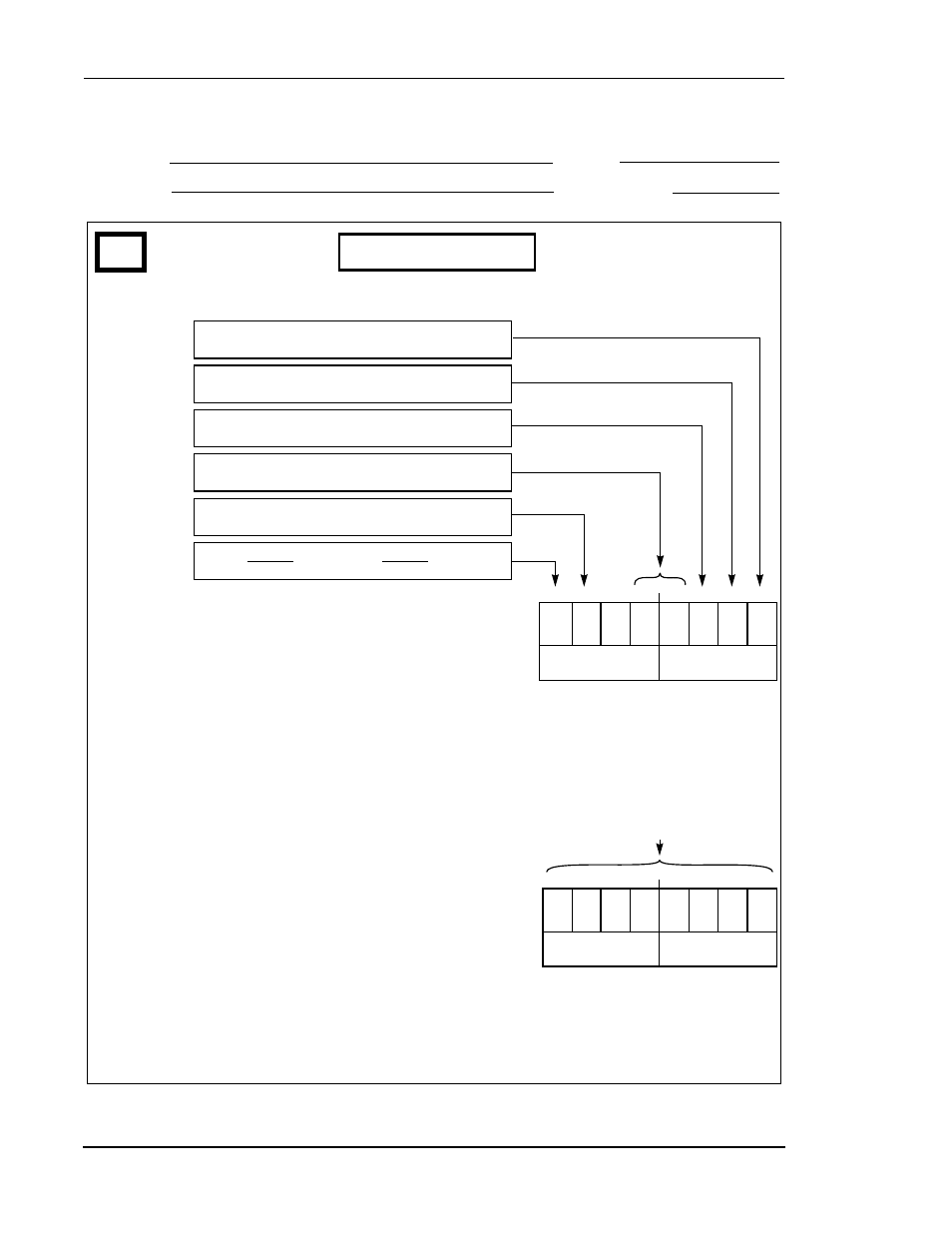

TXDE

TRDY

RXDF

HF3

HF2

6

5

4

3

2

1

0

7

* = Reserved, write as 0

*

0

HOREQ

Interrupt Status Register (ISR)

Interrupt Status Register (ISR)

$2 Read/Write

Reset = $06

Host Flags (HF3, HF2)

Read Only

Host Request (HOREQ)

0 = HOREQ deasserted/1 = HOREQ asserted

DMA

IV1

IV5

IV0

IV4

IV3

6

5

4

3

2

1

0

7

* = Reserved, write as 0

IV7

Interrupt Vector Register (IVR)

IV2

Receive Data Register Full (RXDF)

0 = wait/1 = read

Transmit Data Register Empty (TXDE)

0 = wait/1 = write

DMA Status (DMA)

0 = DMA disabled/1 = DMA enabled

Transmitter Ready (TRDY)

0 = data in HI/1 = data not in HOST8

Interrupt Vector Register (IVR)

$3 Read/Write

Reset = $0F

Interrupt Vector Number For Use By MC68000

Processor Family Vectored Interrupts.

IV6

Processor Side

HI