6 dsp interrupts, Dsp interrupts -20 – Motorola DSP56012 User Manual

Page 100

4-20

DSP56012 User’s Manual

MOTOROLA

Parallel Host Interface

Host Interface (HI)

4.4.4.6

DSP Interrupts

The HI interface can request interrupt service from either the DSP or the host

processor. The DSP interrupts are internal and do not require the use of an external

interrupt pin (see

on page 4-23). When the appropriate mask bit in the

HCR is set, an interrupt condition caused by the host processor sets the appropriate

bit in the HSR, which generates an interrupt request to the DSP. The DSP

acknowledges interrupts caused by the host processor by jumping to the appropriate

interrupt service routine. The three possible interrupts are:

1. receive data register full,

2. transmit data register empty, and

3. host command.

The host command can access any interrupt vector in the interrupt vector table

although it has a set of vectors reserved for host command use. The DSP interrupt

service routine must read or write the appropriate HI register (clearing HRDF or

HTDE, for example) to clear the interrupt.

Note:

In the case of host command interrupts, the interrupt acknowledge from the

program controller clears the pending interrupt condition.

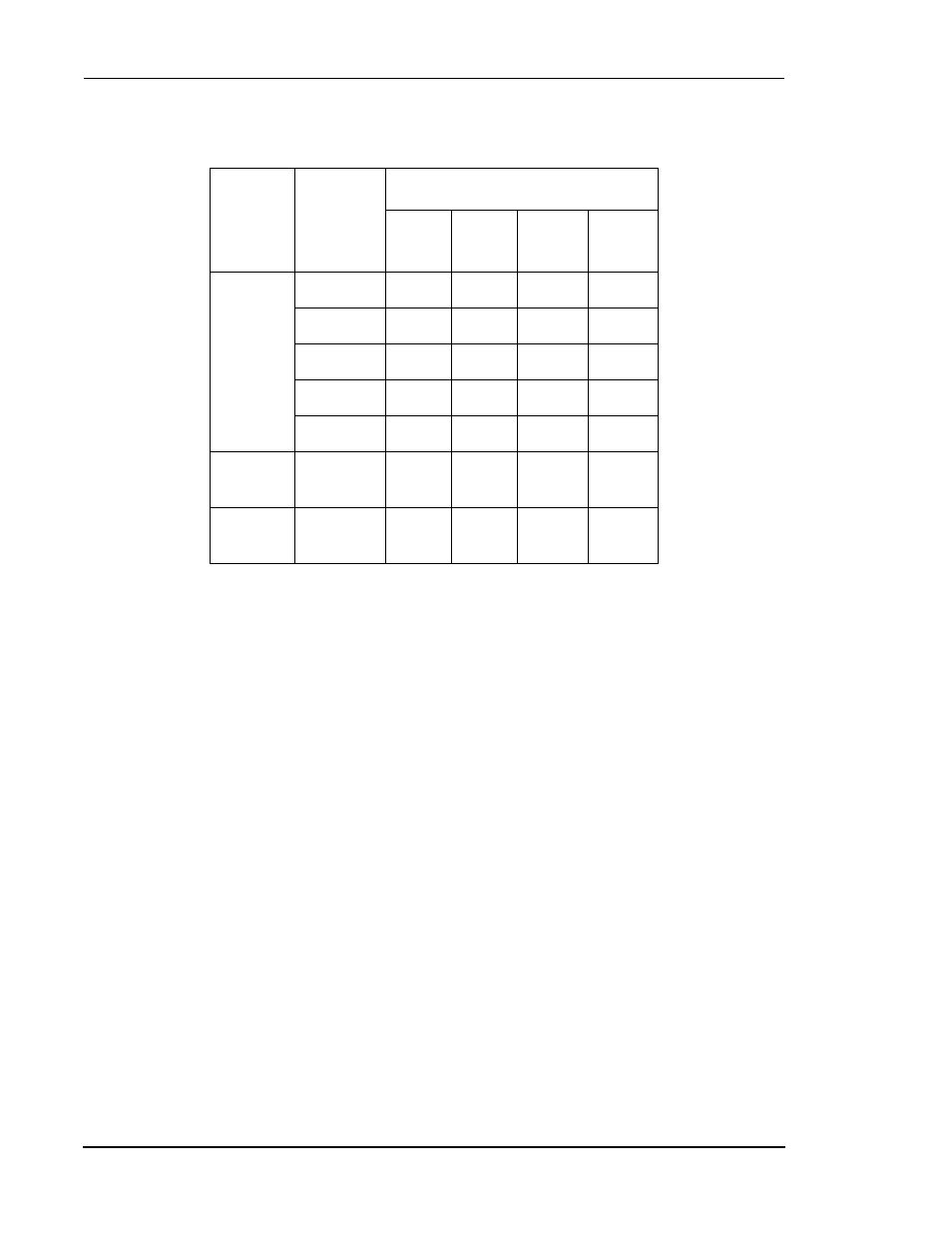

HSR

X:$FFE9

DMA

0

0

0

0

HF[1:0]

0

0

0

0

HCP

0

0

0

0

HTDE

1

1

1

1

HRDF

0

0

0

0

HORX

X:$FFEB

HORX

[23:0]

—

—

—

—

HOTX

X:$FFEB

HOTX

[23:0]

—

—

—

—

Table 4-1

HI Registers after Reset—DSP CPU Side (Continued)

Register

Name

Register

Data

Reset Type

HW

Reset

SW

Reset

IR

Reset

ST

Reset