7 phase lock loop (pll) configuration, Phase lock loop (pll) configuration -19, Phase lock loop (pll) configuration -18 – Motorola DSP56012 User Manual

Page 79

Memory, Operating Modes, and Interrupts

Phase Lock Loop (PLL) Configuration

MOTOROLA

DSP56012 User’s Manual

3-19

3.7

PHASE LOCK LOOP (PLL) CONFIGURATION

Section 9 of the

DSP56000 Family Manual

provides detailed information about the

PLL. The information included here is a brief overview of the PLL.

The PLL is configured and controlled by bits in the PLL Control Register (PCTL). The

PLL Multiplication Factor and the clock applied to EXTAL determine the frequency

at which the Voltage Controlled Oscillator (VCO) will oscillate, that is, the output

frequency of the PLL.

If the PLL is used as the DSP internal clock (PCTL bit PEN = 1):

• the PLL VCO output is used directly as the internal DSP clock if the PCTL

Chip Clock Source Bit (CSRC) is set, and

• the PLL VCO frequency is divided by the Low Power Divider (LPD) and then

used as the internal DSP clock if the CSRC bit is cleared.

The DSP56012 PLL Multiplication Factor is set to 3 during hardware reset, which

means that the Multiplication Factor bits (MF1[1:0] in the PCTL) are set to $002. The

PLL may be disabled (PEN = 0) upon reset by pulling the PINIT pin low. The DSP

will subsequently operate at the frequency of the clock applied to the EXTAL pin

until the PEN bit is set. This reset value cannot be modified by the user until the DSP

comes out of Reset. The DSP56012 LPD Division Factor bits (DF[3:0] in the PCTL) are

cleared during hardware reset. Once the PEN bit is set, it cannot be cleared by

software.

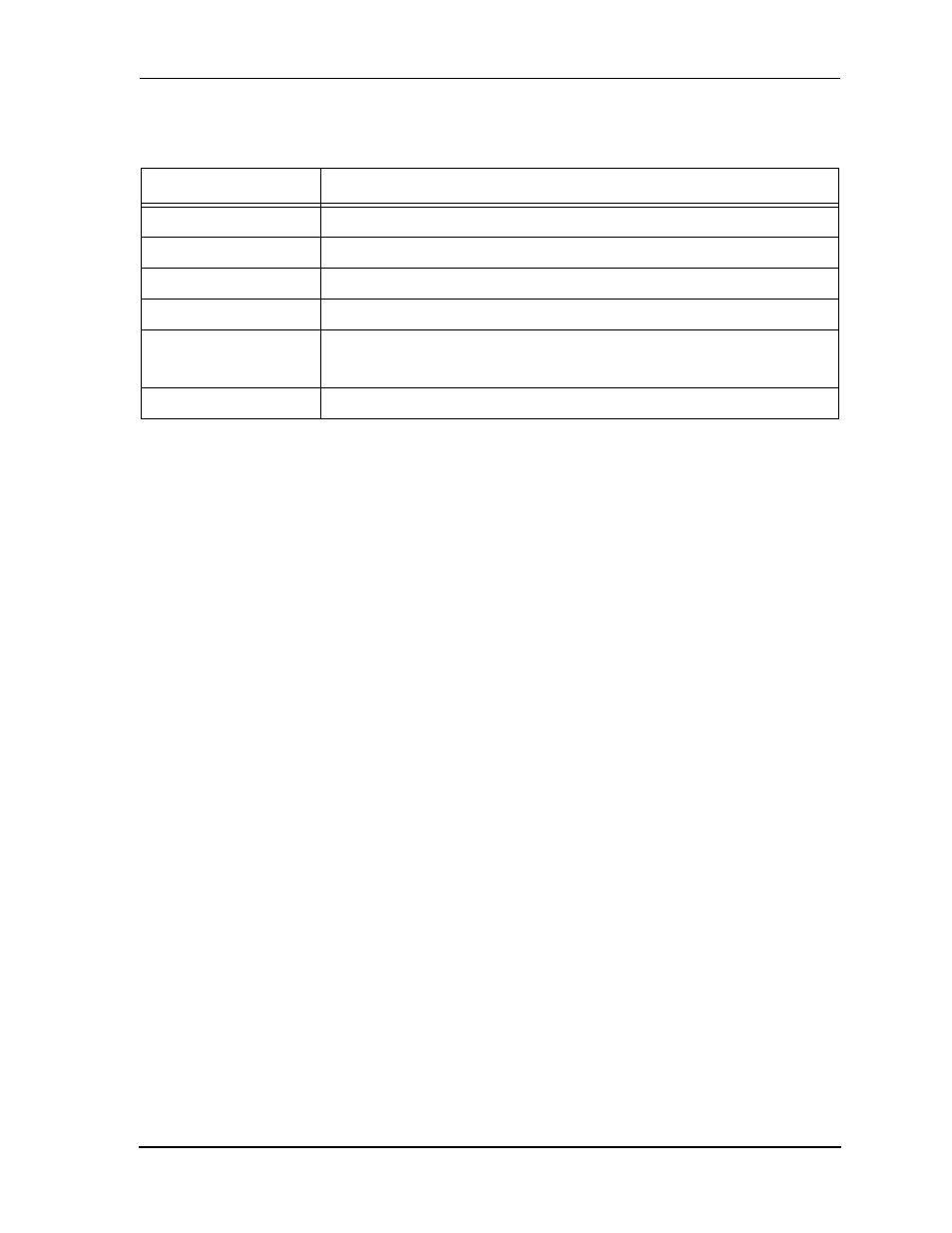

P: $0052

DAX Block Transferred

P: $0054

Reserved

P: $0056

DAX Transmit Register Empty

P: $0058

Reserved

.

.

.

.

.

.

P: $007E

Reserved

Table 3-5

Interrupt Vectors (Continued)

Address

Interrupt Source