4 phase lock loop (pll), Table24 phase lock loop signals, Phase lock loop (pll) -7 – Motorola DSP56012 User Manual

Page 47: Table 2-4, Phase lock loop signals -7

Signal Descriptions

Phase Lock Loop (PLL)

MOTOROLA

DSP56012 User’s Manual

2-7

2.4

PHASE LOCK LOOP (PLL)

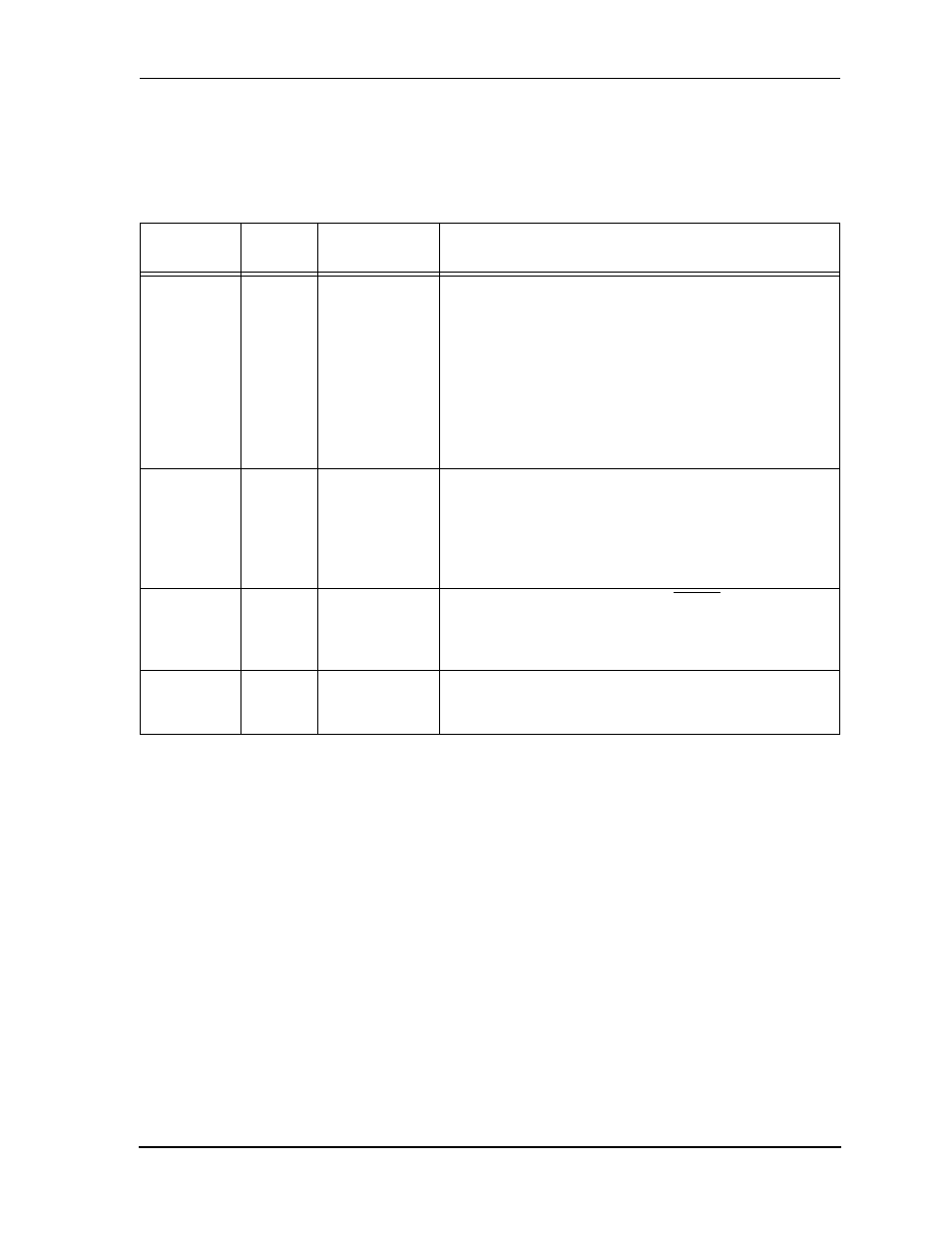

Table 2-4

Phase Lock Loop Signals

Signal Name

Type

State During

Reset

Signal Description

PLOCK

Output

Indeterminate

Phase Locked

—PLOCK is an output signal that, when

driven high, indicates that the PLL has achieved phase

lock. After Reset, PLOCK is driven low until lock is

achieved.

Note:

PLOCK is a reliable indicator of the PLL lock

state only after the chip has exited the Reset

state. During hardware reset, the PLOCK state is

determined by PINIT and the current PLL lock

condition.

PCAP

Input

Input

PLL Capacitor

—PCAP is an input connecting an off-chip

capacitor to the PLL filter. Connect one capacitor

terminal to PCAP and the other terminal to V

CCP

.

If the PLL is not used, PCAP may be tied to V

CC

, GND,

or left floating.

PINIT

Input

Input

PLL Initial

—During assertion of RESET, the value of

PINIT is written into the PLL Enable (PEN) bit of the PLL

Control Register, determining whether the PLL is

enabled or disabled.

EXTAL

Input

Input

External Clock/Crystal Input

—EXTAL interfaces the

internal crystal oscillator input to an external crystal or

an external clock.