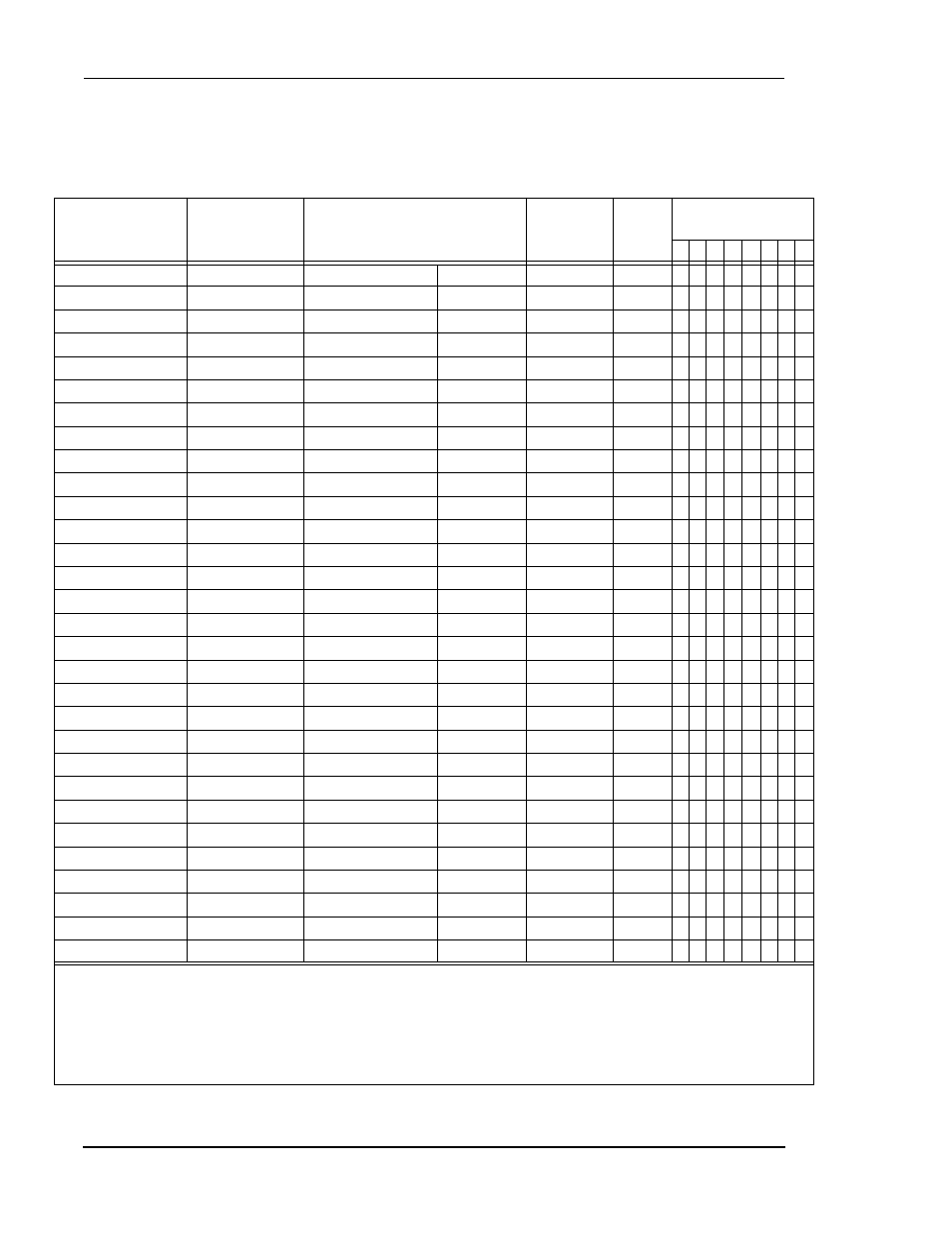

Tableb3 instruction set summary (sheet 7 of 7), Table b-3 – Motorola DSP56012 User Manual

Page 240

B-8

DSP56012 User’s Manual

MOTOROLA

Programming Reference

Table B-3

Instruction Set Summary (Sheet 1 of 7)

Mnemonic

Syntax

Parallel Moves

Instruction

Program

Words

Osc.

Clock

Cycles

Status Request

Bits:

S L E U N Z V C

ABS

D (parallel

move)

1+mv

2+mv

* * * * * * * -

ADC

S,D

(parallel move)

1+mv

2+mv

* * * * * * * *

ADD

S,D (parallel

move)

1+mv

2+mv

* * * * * * * *

ADDL

S,D

(parallel move)

1+mv

2+mv

* * * * * * ? *

ADDR

S,D

(parallel move)

1+mv

2+mv

* * * * * * * *

AND

S,D

(parallel move)

1+mv

2+mv

* * - - ? ? 0 -

AND(I)

#xx,D

1

2

? ? ? ? ? ? ? ?

ASL

D

(parallel move)

1+mv

2+mv

* * * * * * ? ?

ASR

D

(parallel move)

1+mv

2+mv

* * * * * * 0 ?

BCHG

#n,X:

1+ea

4+mvb ? ? ? ? ? ? ? ?

#n,X:

#n,X:

#n,Y:

#n,Y:

#n,Y:

#n,D

BCLR

#n,X:

1+ea

4+mvb ? ? ? ? ? ? ? ?

#n,X:

#n,X:

#n,Y:

#n,Y:

#n,Y:

#n,D

BSET

#n,X:

1+ea

4+mvb ? ? ? ? ? ? ? ?

#n,X:

#n,X:

#n,Y:

#n,Y:

#n,Y:

#n,D

- indicates that the bit is unaffected by the operation

* indicates that the bit may be set according to the definition, depending on parallel move conditions

? indicates that the bit is set according to a special definition; see the instruction descriptions in Appendix A of

the

DSP56000 Family Manual (DSP56KFAMUM/AD)

0 indicates that the bit is cleared