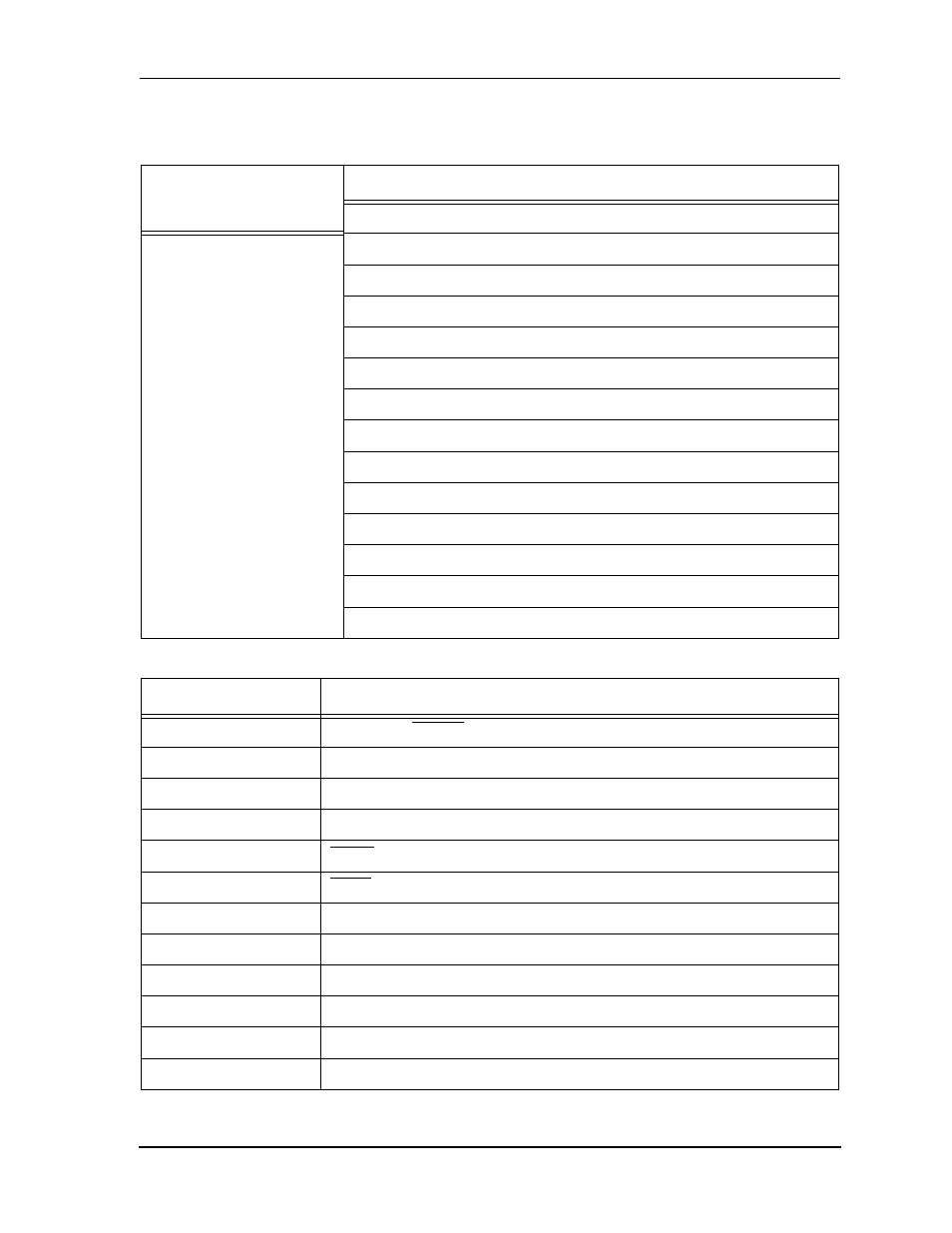

Table35 interrupt vectors (continued), Table 3-5, Interrupt vectors -17 – Motorola DSP56012 User Manual

Page 77

Memory, Operating Modes, and Interrupts

Interrupt Priority Register

MOTOROLA

DSP56012 User’s Manual

3-17

SAI Right Channel Receiver

SAI Right Channel Transmitter

SHI Bus Error

SHI Receive Overrun Error

SHI Transmit Underrun Error

SHI Receive FIFO Full

SHI Transmit Data

SHI Receive FIFO Not Empty

HOST Command Interrupt

HOST Receive Data Interrupt

HOST Transmit Data Interrupt

DAX Transmit Underrun Error

DAX Block Transferred

Lowest

DAX Transmit Register Empty

Table 3-5

Interrupt Vectors

Address

Interrupt Source

P: $0000

Hardware RESET

P: $0002

Stack Error

P: $0004

Trace

P: $0006

SWI

P: $0008

IRQA

P: $000A

IRQB

P: $000C

Reserved

P: $000E

Reserved

P: $0010

SAI Left Channel Transmitter if TXIL = 0

P: $0012

SAI Right Channel Transmitter if TXIL = 0

P: $0014

SAI Transmitter Exception if TXIL = 0

P: $0016

SAI Left Channel Receiver if RXIL = 0

Table 3-4

Interrupt Priorities (Continued)

Priority

Interrupt