Figure54 shi programming model—dsp side, Figure 5-4, Shi programming model—dsp side -6 – Motorola DSP56012 User Manual

Page 154: Figure 5-4 shi programming model—dsp side

5-6

DSP56012 User’s Manual

MOTOROLA

Serial Host Interface

Serial Host Interface Programming Model

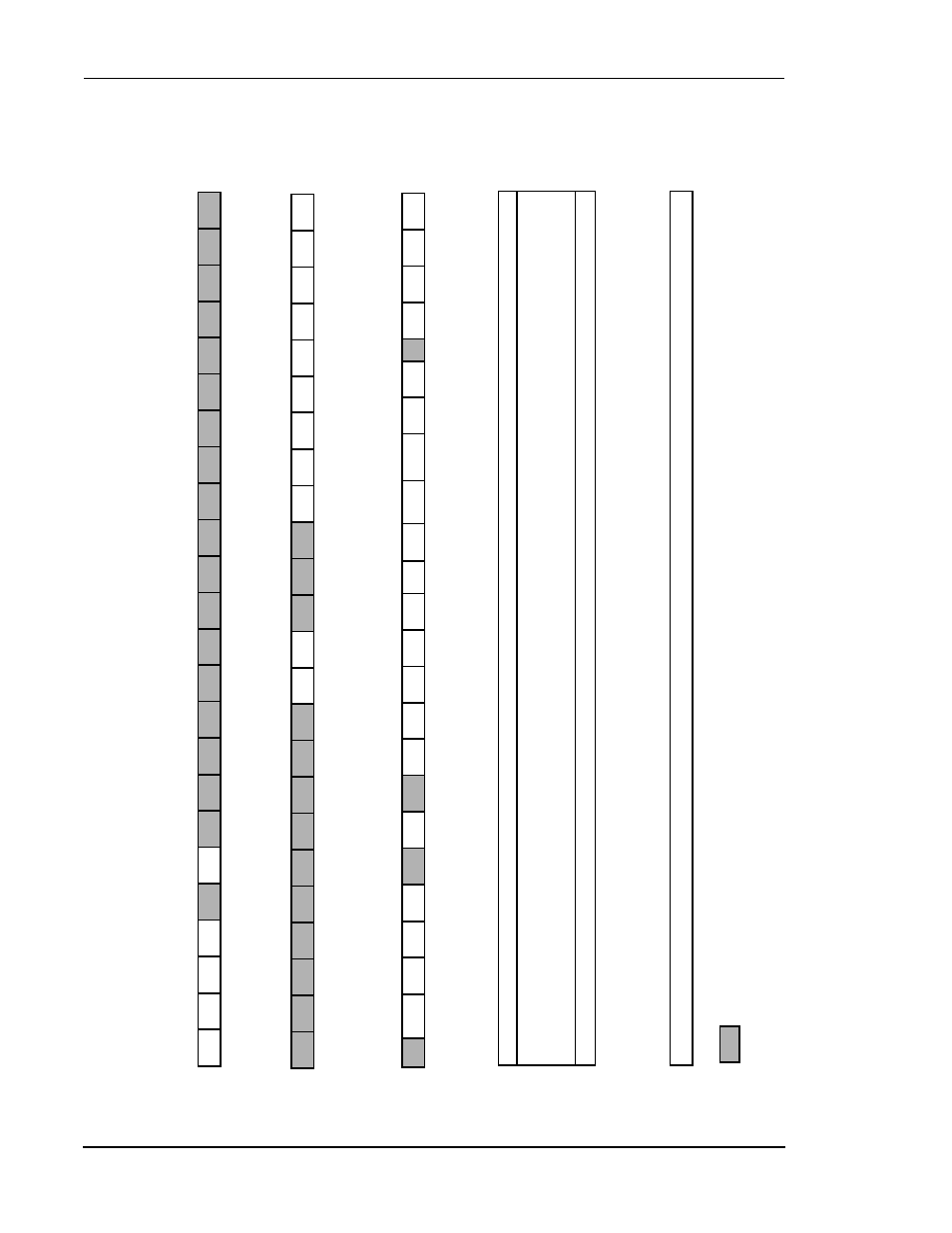

Figure 5-4

SHI Programming Model—DSP Side

8

15

14

13

12

11

10

9

16

23

22

21

20

19

18

17

0

23

SHI Receive Data FIFO (HRX)

(read only, X: $FFF3)

HRX

SHI Transmit Data Register (HTX)

(write only, X: $FFF3)

Reserved bit, read as 0, should be written with 0 for future compatibility.

HDM5

HFM1

0

7654321

HFM0

HDM2

HDM0

HDM1

HRS

HDM3

HDM4

CPHA

CPOL

SHI Clock Control Register (HCKR)

X: $FFF0

0

23

HTX

8

15

14

13

12

11

10

9

16

23

22

21

20

19

18

17

HEN

0

7

6

5

4

321

HM1

HI

2

C

HM0

HRQE0

HMST

HRNE

HBER

HRFF

HROE

HBUSY

HRQE1

HIDLE

SHI Control/Status Register (HCSR)

HRIE0

HRIE1

HTUE

HTDE

HTIE

X: $FFF1

FIFO (10 Words Deep)

HBIE

HFIFO

8

15

14

13

12

11

10

9

16

23

22

21

20

19

18

17

HA6

0

7654321

HA3

HA4

HA5

SHI I

2

C Slave Address Register (HSAR)

X: $FFF2

HA1

AA0419k