Figure425 bits used for host-to-dsp transfer, Figure 4-25, Bits used for host-to-dsp transfer -48 – Motorola DSP56012 User Manual

Page 128: Figure 4-25 bits used for host-to-dsp transfer, Parallel host interface host interface (hi)

4-48

DSP56012 User’s Manual

MOTOROLA

Parallel Host Interface

Host Interface (HI)

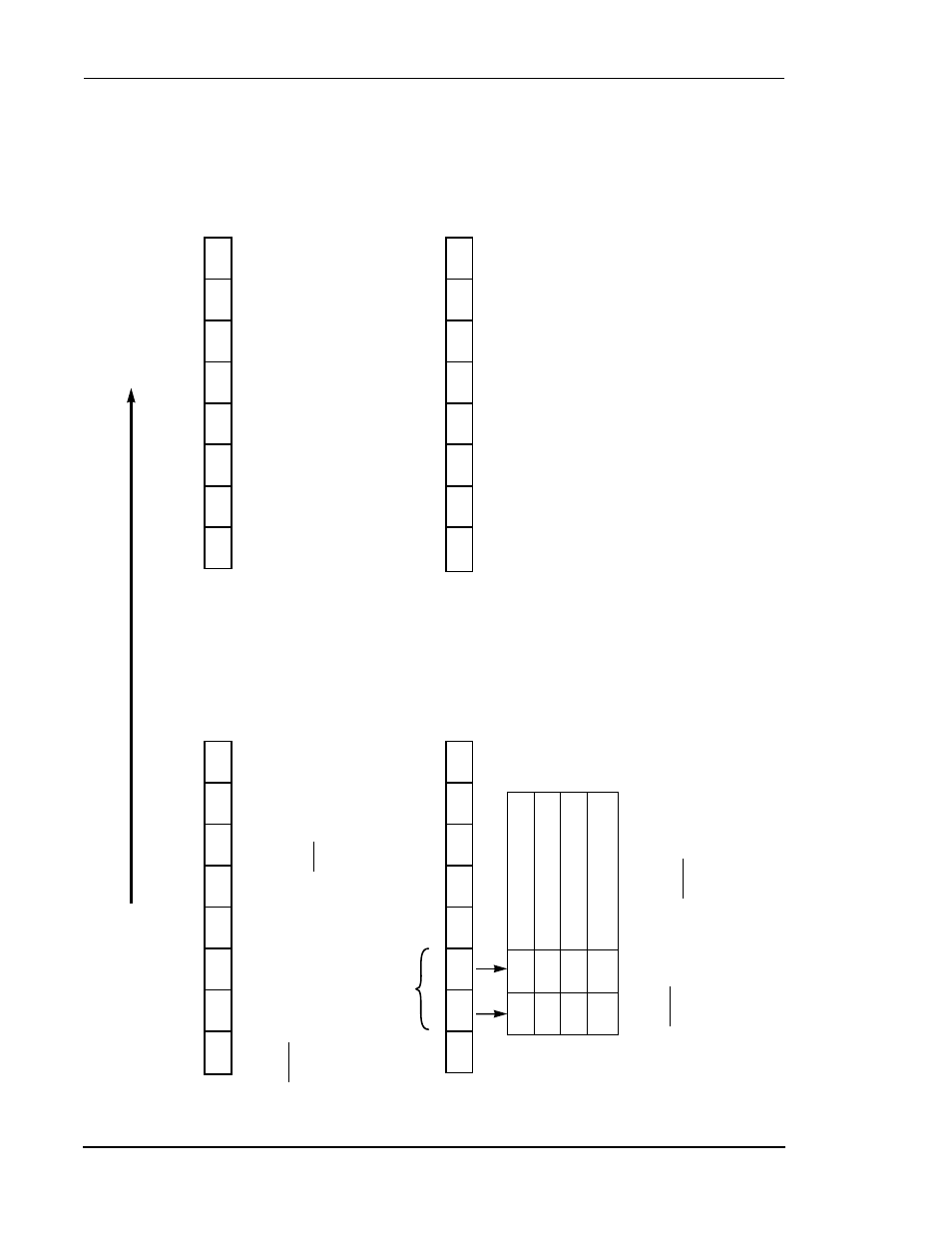

Figure 4-25

Bits Used for Host-to-DSP Transfer

0

0

Interrupt Mode (DMA Off)

0

1

24 Bit DMA Mode

1

0

16 Bit DMA Mode

11

8 Bit DMA Mode

$2

INTERRUPT

STATUS

REGISTER (ISR)

(READ ONLY)

$0

HOST

DSP56012

TXDE—TRANSMIT DATA REGISTER EMPTY

1 = INDICATES THE TRANSMIT BYTE REGISTERS (TXH, TXM, TXL) ARE EMPTY.

0 = CLEARED BY WRITING TO TXL; TXDE CAN BE USED TO ASSERT THE

HOREQ

PIN.

TRDY—TRANSMITTER READY = TXDE • HRDF

1 = BOTH THE TRANSMIT BYTE REGISTERS AND THE HOST RECEIVE DATA

REGISTERS ARE EMPTY.

0 = ONE OR BOTH REGISTERS ARE FULL.

X:$FFE9

HOST STATUS

REGISTER (HSR)

(READ ONLY)

HRDF—HOST RECEIVE DATA FULL

1 = THE HOST RECEIVE REGISTER (HORX) CONTAINS DATA FROM THE

HOST PROCESSOR.

0 = HORX IS EMPTY.

DMA —INDICATES THE HOST PROCESSOR HAS ENABLED THE DMA MODE

1 = DMA ON.

0 = HOST MODE.

HOST CONTROL

REGISTER (HCR)

(READ/WRITE)

HRIE—HOST RECEIVE INTERRUPT ENABLE

ENABLES INTERRUPT AT P:$0030

DSP INTERRUPT IS CAUSED BY HRDF = 1

1 = INTERRUPT P:$0030 ENABLED.

0 = INTERRUPT P:$0030 DISABLED.

TREQ—TRANSMIT REQUEST ENABLE

USED TO ENABLE INTERRUPTS THAT COME FROM TXDE TO THE HOST

VIA THE HOREQ

PIN.

1 = TXDE INTERRUPTS PASS TO HOREQ

.

0 = TXDE INTERRUPTS ARE MASKED.

INTERRUPT

CONTROL

REGISTER (ICR)

(READ/WRITE)

X:$FFE8

HOREQ

0

HF3

TRDY

TXDE

70

HF3

DMA

6

5

432

1

HF2

DMA

HF1

HF0

HTDE

HRDF

70

0

0

6

5

432

1

HCP

INIT

HF1

HF0

TREQ

RREQ

70

HM0

HM1

6

5

432

1

0

HOREQ

HF1

HF0

TREQ

RREQ

70

HM0

HM1

6

5

432

1

TREQ

MODES

AA0333