3 internal i/o memory map, Table32 internal i/o memory map (continued), Internal i/o memory map -10 – Motorola DSP56012 User Manual

Page 70: Table 3-2, Internal i/o memory map -9

3-10

DSP56012 User’s Manual

MOTOROLA

Memory, Operating Modes, and Interrupts

DSP56012 Data and Program Memory Maps

ANDI

#$F3,OMR

; Clear PEA/PEB bit in OMR

ANDI

#$FC,MR

; Allow a delay for remapping,

; meanwhile re-enable interrupts

JMP

>Next_Address

; 2-word (long) jump instruction (uninterruptable)

Note:

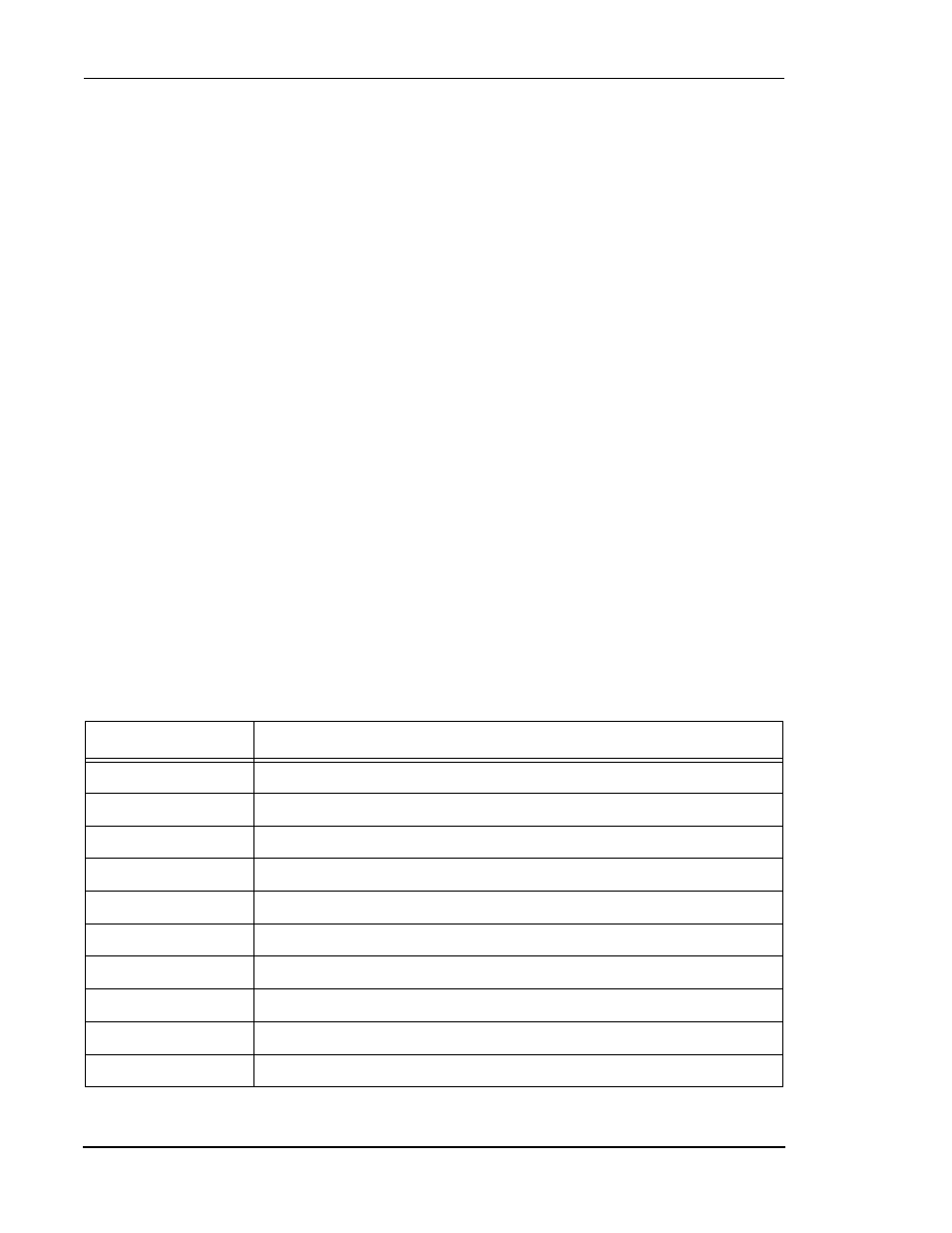

“Next_Address” is any valid program address in the new memory 3.3.3 Internal I/O Memory Map The DSP56012 on-chip peripheral modules have their registers mapped to the Note: Location X:$FFFE is the Bus Control Register (BCR) for the DSP56000 Table 3-2 Internal I/O Memory Map Location Register X: $FFFF Interrupt Priority Register (IPR) X: $FFFE Reserved X: $FFFD PLL Control Register (PCTL) X: $FFFC Reserved X: $FFFB Reserved X: $FFFA Reserved X: $FFF9 Reserved X: $FFF8 Reserved X: $FFF7 GPIO Control/Data Register (GPIOR) X: $FFF6 Reserved

configuration (after the switch). The two-word instruction “JMP

>Next_Address” can be replaced by a sequence of an NOP followed by

a one-word “JMP

OMR with PE modified (ORI/ANDI/MOVEC), followed by an NOP as

a delay for remapping, and then followed by a JMP >long (or another

NOP and JMP

addresses in the internal I/O memory range, as shown in

core. Although labelled “Reserved” on the DSP56012, the BCR remains

active. The BCR is cleared by reset and should remain cleared (i.e., do

not write to this location) since the DSP56012 does not make use of the

BCR function.