1 port pin register descriptions, 6 .1 port pin register descriptions -3, Maxq610 user’s guide – Maxim Integrated MAXQ610 User Manual

Page 96

6-3

MAXQ610 User’s Guide

All these special functions are disabled by default with the exception of the JTAG interface pins, which are enabled

by default following any reset .

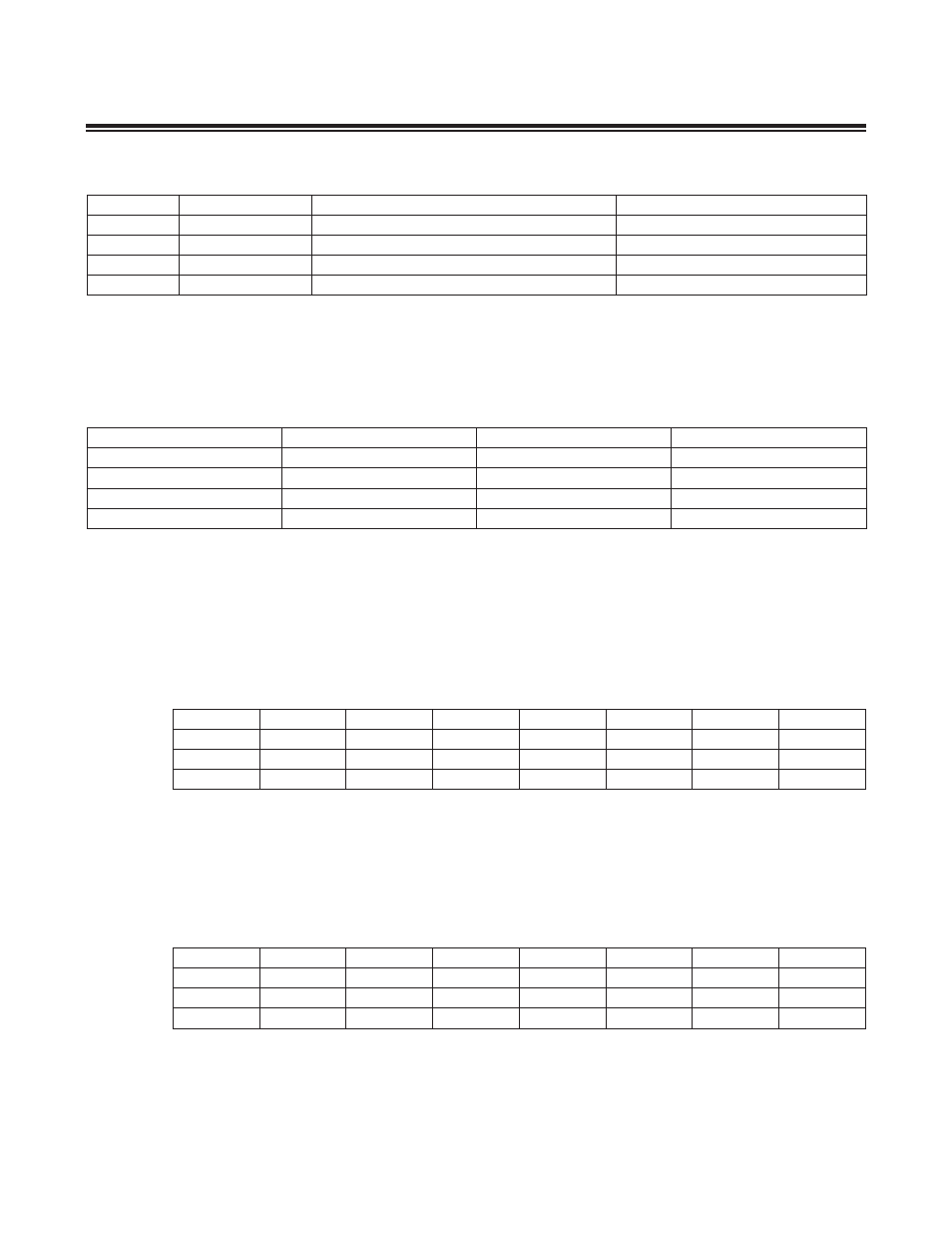

The port pin input/output states can be defined as shown in Table 6-2 .

Table 6-2. MAXQ610 Port Pin Input/Output States

Table 6-1. Port Pin Special Functions (continued)

6.1 Port Pin Register Descriptions

The following peripheral registers are used to control the general-purpose I/O and external interrupt features specific

to the MAXQ610 .

Bits 7:0: Port 0 Output. This register stores the data that is output on any of the pins of port 0 that have been defined

as output pins . If the port pins are in input mode, this register controls the weak pullup enable for each pin . Changing

the data direction of any pins for this port (through register PD0) does not affect the value in this register .

Bits 7:0: Port 1 Output. This register stores the data that is output on any of the pins of port 1 that have been defined

as output pins . If the port pins are in input mode, this register controls the weak pullup enable for each pin . Changing

the data direction of any pins for this port (through register PD0) does not affect the value in this register .

PORT PIN

DIRECTION

SPECIAL FUNCTION

ENABLED WHEN

P4 .2

Input/Output

—

—

P4 .3

Input/Output

—

—

P4 .4

Input/Output

—

—

P4 .5

Input/Output

—

—

PDx.y

POx.y

PORT PIN MODE

PORT PIN (Px.y) STATE

0

0

Input

Three-state

0

1

Input

Weak pullup HIGH

1

0

Output

Strong drive LOW

1

1

Output

Strong drive HIGH

Register Name

PO0

Register Description

Port 0 Output Register

Register Address

M0[00h]

Register Name

PO1

Register Description

Port 1 Output Register

Register Address

M0[01h]

Bit #

7

6

5

4

3

2

1

0

Name

PO0 .7

PO0 .6

PO0 .5

PO0 .4

PO0 .3

PO0 .2

PO0 .1

PO0 .0

Reset

s

s

s

s

s

s

s

s

Access

rw

rw

rw

rw

rw

rw

rw

rw

Bit #

7

6

5

4

3

2

1

0

Name

PO1 .7

PO1 .6

PO1 .5

PO1 .4

PO1 .3

PO1 .2

PO1 .1

PO1 .0

Reset

s

s

s

s

s

s

s

s

Access

rw

rw

rw

rw

rw

rw

rw

rw