Maxq610 user’s guide – Maxim Integrated MAXQ610 User Manual

Page 69

4-14

MAXQ610 User’s Guide

REGISTER

DESCRIPTION

WDCN.6 (EWDI)

Watchdog Interrupt Enable. If this bit is set to 1, an interrupt request can be generated

when the WDIF bit is set to 1 by any means . If this bit is cleared to 0, no interrupt occurs

when WDIF is set to 1, however, it does not stop the watchdog timer or prevent watch-

dog resets from occurring if EWT = 1 . If EWT = 0 and EWDI = 0, the watchdog timer is

stopped . If the watchdog timer is stopped (EWT = 0 and EWDI = 0), setting the EWDI bit

resets the watchdog interval and reset counter, and enables the watchdog timer .

This bit is cleared to 0 by power-fail and power-on reset and is unaffected by other forms

of reset .

WDCN.7 (POR)

Power-on Reset Flag. This bit is set to 1 anytime when V

DD

is below the V

POR

threshold .

This bit must be cleared by software . This bit is unaffected by resets and is set to 1 by

hardware only by POR (V

DD

< V

POR

) .

A[n], 09h[nh]

Accumulator n Register (16 bits)

Initialization

This register is cleared to 0000h on all forms of reset .

Access

Unrestricted direct read/write access .

A[n].15 to A[n].0

This register acts as the accumulator for all ALU arithmetic and logical operations when

selected by the accumulator pointer (AP) . It can also be used as a general-purpose work-

ing register .

PFX[n], 0Bh[nh]

Prefix Register (16 bits)

Initialization

This register is cleared to 0000h on all forms of reset .

Access

Unrestricted direct read/write access .

PFX[n].15 to PFX[n].0

The prefix register provides a means of supplying an additional 8 bits of high-order data

for use by the succeeding instruction as well as providing additional indexing capabilities .

This register only holds any data written to it for one execution cycle, after which it reverts

to 0000h . Although this is a 16-bit register, only the lower 8 bits are actually used for pre-

fixing purposes by the next instruction .

Writing to or reading from any index in the prefix module selects the same 16-bit register .

However, when the prefix register is written, the index n used for the PFX[n] write also

determines the high-order bits for the register source and destination specified in the fol-

lowing instruction .

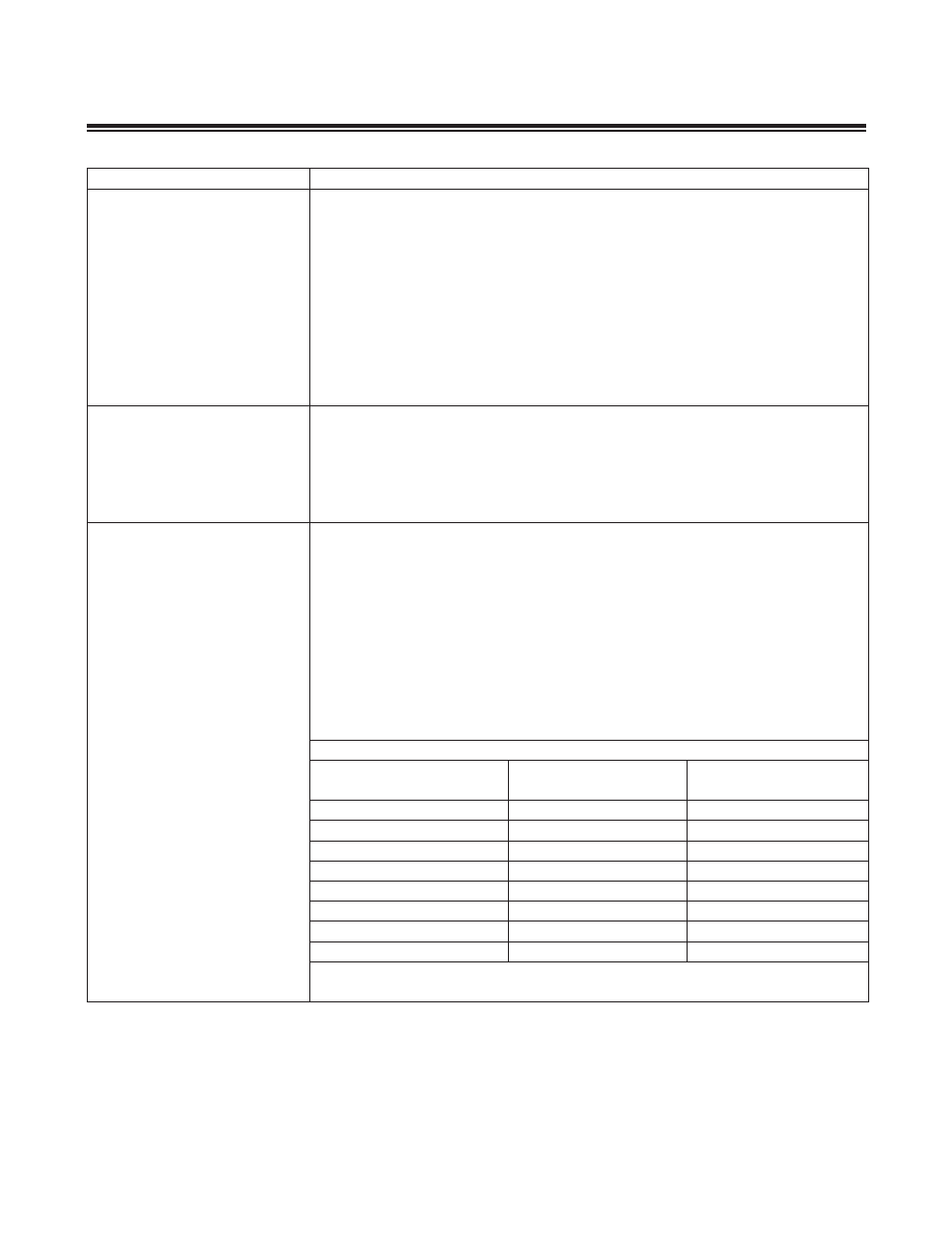

SOURCE, DESTINATION INDEX SELECTION

WRITE TO

SOURCE REGISTER

RANGE

DESTINATION REGISTER

RANGE

PFX[0]

00h to 0Fh

00h to 07h

PFX[1]

10h to 1Fh

00h to 07h

PFX[2]

00h to 0Fh

08h to 0Fh

PFX[3]

10h to 1Fh

08h to 0Fh

PFX[4]

00h to 0Fh

10h to 17h

PFX[5]

10h to 1Fh

10h to 17h

PFX[6]

00h to 0Fh

18h to 1Fh

PFX[7]

10h to 1Fh

18h to 1Fh

The index selection reverts to 0 (default mode allowing selection of registers 0h to 7h for

destinations) after one cycle in the same manner as the contents of the prefix register .