2 breakpoint registers, 1 breakpoint n register (bpn, n = 0 to 3), 2 breakpoint 4 register (bp4) – Maxim Integrated MAXQ610 User Manual

Page 156: 12 .2 breakpoint registers -5, Maxq610 user’s guide, Table 12-1. background mode commands (continued)

12-5

MAXQ610 User’s Guide

12.2 Breakpoint Registers

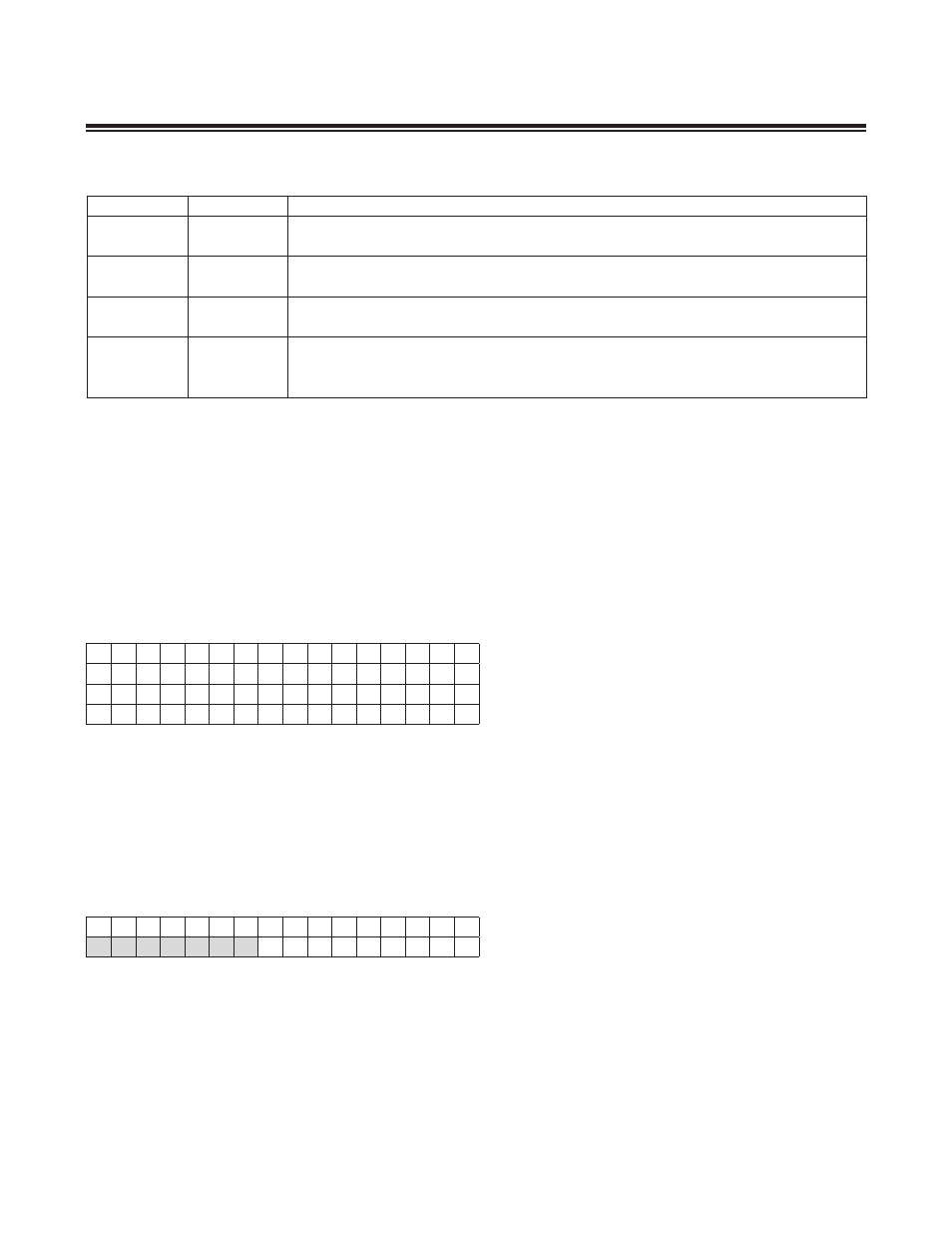

The MAXQ610 microcontroller incorporates six breakpoint registers (BP0 to BP5) that are configurable by the host

for establishing different types of breakpoint mechanisms . The first four breakpoint registers (BP0 to BP3) are 16-bit

registers that are configurable as program memory address breakpoints . When enabled, the debug engine forces a

break when a match between the breakpoint register and the program memory execution address occurs . The final

two 16-bit breakpoint registers (BP4, BP5) are configurable in one of two possible capacities . They can be configured

as data memory address breakpoints or can be configured to support register access breakpoints . In either case, if

breakpoints are enabled and the defined breakpoint match occurs, the debug engine generates a break condition .

12.2.1 Breakpoint n Register (BPn, n = 0 to 3)

These registers are accessible only through background mode read/write commands . These four registers serve as

program memory address breakpoints . When DME bit is set in background mode, the debug engine monitors the

program address bus activity while the CPU is executing the user program . If an address match is detected, a break

occurs, allowing the debug engine to take control of the CPU and enter debug mode .

12.2.2 Breakpoint 4 Register (BP4)

This register is accessible only through background mode read/write commands .

When (REGE = 0): This register serves as one of the two data memory address breakpoints . When DME is set in

background mode, the debug engine monitors the data memory address bus activity while the CPU is executing the

Table 12-1. Background Mode Commands (continued)

**Module Specifier 3:0 {0 to 15}

*Register Index within Module {0 to 31}

OP CODE

COMMAND

OPERATION

0001–1000

Write BP3

Write data to the BP3 . The contents of ICDB are loaded into the BP3 register by the debug

engine at the end of data transfer cycles . Data is transferred with the least significant byte first .

0001–1001

Write BP4

Write data to the BP4 . The contents of ICDB are loaded into the BP4 register by the debug

engine at the end of data transfer cycles . Data is transferred with the least significant byte first .

0001–1010

Write BP5

Write data to the BP5 . The contents of ICDB are loaded into the BP5 register by the debug

engine at the end of data transfer cycles . Data is transferred with the least significant byte first .

0001–1111

Debug

Debug command . This command forces the debug engine into debug mode and halts the

CPU operation at the completion of the current instruction after the debug command is recog-

nized by the debug engine .

15

0

Breakpoint 0 Register (BP0)

Breakpoint 1 Register (BP1)

Breakpoint 2 Register (BP2)

Breakpoint 3 Register (BP3)

1

s

1

s

1

s

1

s

1

s

1

s

1

s

1

s

1

s

1

s

1

s

1

s

1

s

1

s

1

s

1

s

Power-On Reset and Test-Logic-Reset

Read (r), Write (w), or Special (s) access

15

0

Breakpoint 4 Register (BP4) (REGE = 0)

x

x

x

x

x

x

x

Breakpoint 4 Register (BP4) (REGE = 1)

1

s

1

s

1

s

1

s

1

s

1

s

1

s

1*

s

1*

s

1*

s

1*

s

1*

s

1**

s

1**

s

1**

s

1**

s

Power-On Reset and Test-Logic-Reset

Read (r), Write (w), or Special (s) access