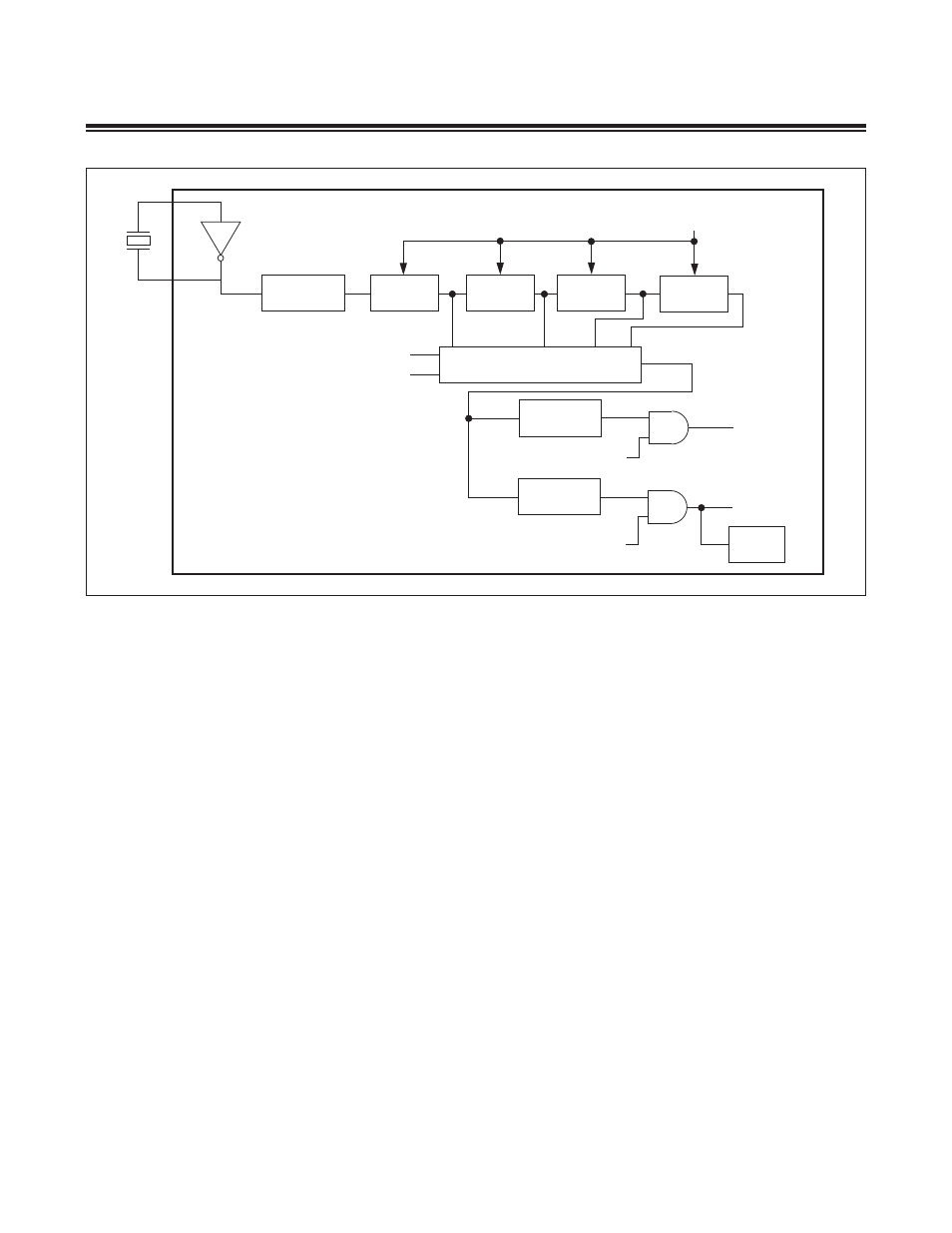

Figure 3-1 . watchdog timer block diagram -19, Maxq610 user’s guide – Maxim Integrated MAXQ610 User Manual

Page 54

3-19

MAXQ610 User’s Guide

If the timeout is reached without RWT being set, hardware generates a watchdog interrupt if the interrupt source has

been enabled . If no further action is taken to prevent a watchdog reset, in the 512 system clock cycles following the

timeout, hardware can reset the CPU if EWT = 1 . When the reset occurs, the watchdog timer reset flag (WTRF =

WDCN .2) is automatically set to indicate the cause of the reset, however, software must clear this bit manually .

The watchdog interrupt is also available for applications that do not need a true watchdog reset, but simply a very

long timer . The interrupt is enabled using the enable watchdog timer interrupt (EWDI = WDCN .6) bit . When the timeout

occurs, the watchdog timer sets the WDIF bit (WDCN .3), and an interrupt occurs if the interrupt global enable (IGE

= IC .0) is set and either 1) the interrupt priority status (IPS[1:0]) bits are set to 11b (idle), or 2) the watchdog timer

interrupt is configured to higher priority than an interrupt currently being serviced . Note that WDIF is set 512 system

clocks before a potential watchdog reset . The watchdog interrupt flag indicates the source of the interrupt, and must

be cleared by software .

Using the watchdog interrupt during software development can allow the user to select ideal watchdog reset locations .

Code is first developed without enabling the watchdog interrupt or reset functions . Once the program is complete,

the watchdog interrupt function is enabled to identify the required locations in code to set the RWT (WDCN .0) bit .

Incrementally adding instructions to reset the watchdog timer prior to each address location (identified by the watch-

dog interrupt) allows the code to eventually run without receiving a watchdog interrupt . At this point the watchdog timer

reset can be enabled without the potential of generating unwanted resets . At the same time the watchdog interrupt can

also be disabled . Proper use of the watchdog interrupt with the watchdog reset allows interrupt software to survey the

system for errant conditions .

When using the watchdog timer as a system monitor, the watchdog reset function should be used . If the interrupt func-

tion were solely used, the purpose of the watchdog would be defeated . For example, assume the system is execut-

ing errant code prior to the watchdog interrupt . The interrupt would temporarily force the system back into control by

vectoring the CPU to the interrupt service routine . Restarting the watchdog and exiting by an RETI or RET would return

the processor to the lost position prior to the interrupt . By using the watchdog reset function, the processor is restarted

from the beginning of the program and therefore placed into a known state .

Figure 3-1. Watchdog Timer Block Diagram

SYSTEM CLOCK

MODE

TIMEOUT

SELECTOR

WD1

HFXOUT

HFXIN

WD0

DIVIDE BY

2

15

DIVIDE BY

2

3

2

15

2

18

2

21

2

24

DIVIDE BY

2

3

WDIF

(WDCN.3)

WTRF

(WDCN.2)

WATCHDOG

INTERRUPT

EWT (WDCN.1)

(ENABLE WATCHDOG TIMER RESET)

EWDI (WDCN.6)

(ENABLE WATCHDOG INTERRUPT)

512 SYSCLK

DELAY

DIVIDE BY

2

3

RWT (WDCN.0)

(RESET WATCHDOG)

TIMEOUT

RESET

MAXQ610