2 serial port mode register (smd), 3 serial port data buffer register (sbuf), 4 serial port phase register (pr) – Maxim Integrated MAXQ610 User Manual

Page 136: Maxq610 user’s guide

9-11

MAXQ610 User’s Guide

Bit 0: Receive Interrupt Flag (RI). This bit indicates that a data byte has been received in the serial port buffer . The

bit is set at the end of the 8th bit for mode 0, after the last sample of the incoming stop bit for mode 1 subject to the

value of the SM2 bit, or after the last sample of RB8 for modes 2 and 3 . This bit must be cleared by software once set .

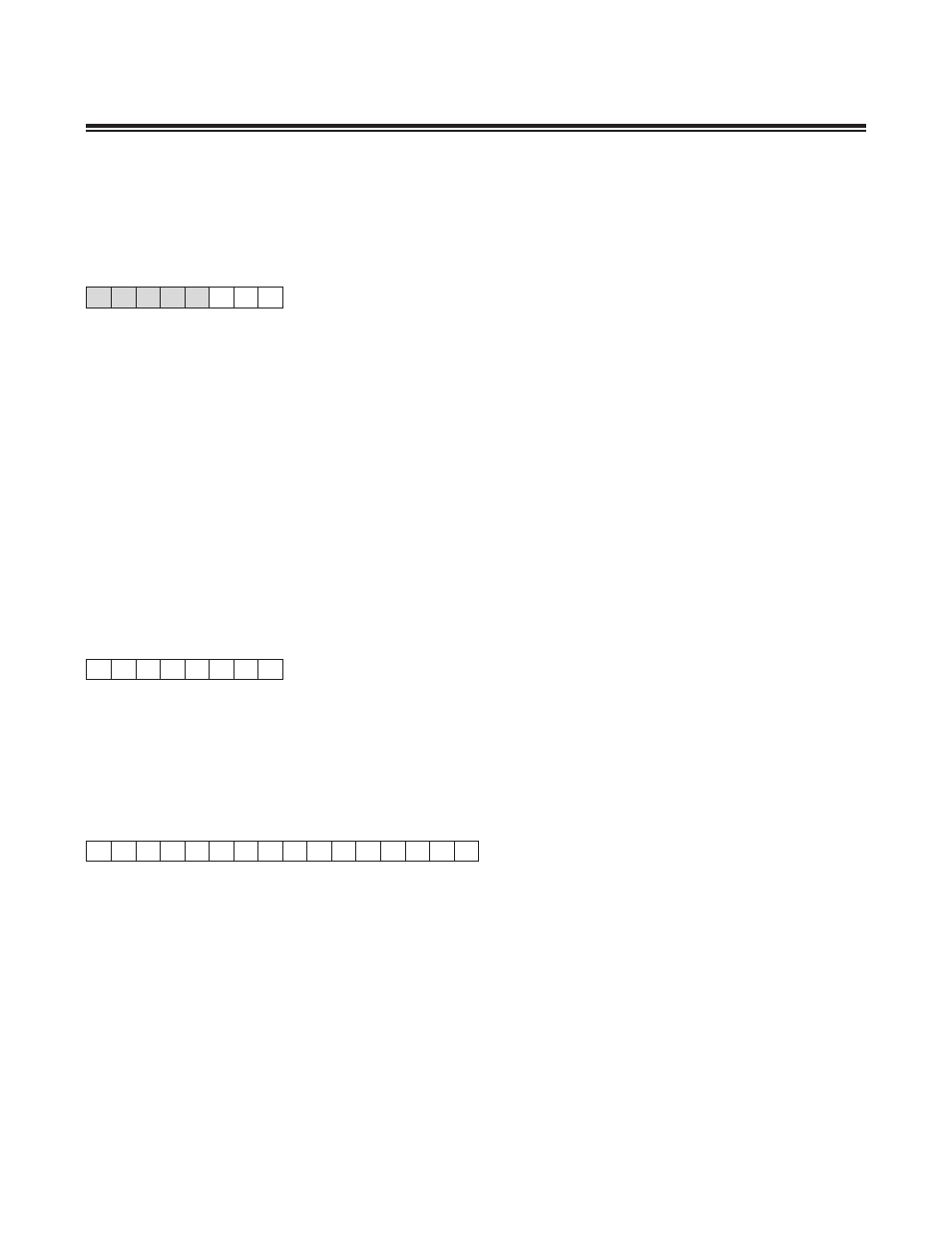

9.4.2 Serial Port Mode Register (SMD)

Bit 3: Enable Serial Port Interrupt (ESI). Setting this bit to 1 enables interrupt requests generated by the RI or TI flags

in SCON . Clearing this bit to 0 disables the serial port interrupt .

Bit 2: Serial-Port Baud-Rate Select (SMOD). The SMOD selects the final baud rate for the asynchronous mode:

1 = 16 times the baud clock for mode 1 and 3

32 times the system clock for mode 2

0 = 64 times the baud clock for mode 1 and 3

64 times the system clock for mode 2

Bit 0: Framing Error Detection Enable (FEDE). This bit selects the function of SM0 (SCON .7):

0 = SCON .7 functions as SM0 for serial-port mode selection

1 = SCON .7 is converted to the framing error (FE) flag

9.4.3 Serial Port Data Buffer Register (SBUF)

Data for serial port is read from or written to this location . The serial transmit and receive buffers are separate but both

are addressed at this location .

9.4.4 Serial Port Phase Register (PR)

This register is used to load and read the value in the phase register .

7

0

— — — — —-

Serial Port Mode Register (SMD)

0

0

0

0

0

0

0

0

Power-On Reset and System Resets

r

r

r

r

r rw rw rw

Read (r), Write (w), or Special (s) access

7

0

Serial Port Data Buffer Register (SBUF)

0

rw

0

rw

0

rw

0

rw

0

rw

0

rw

0

rw

0

rw

Power-On Reset and System Resets

Read (r), Write (w), or Special (s) access

15

0

Serial Port Phase Register (PR)

0

rw

0

rw

0

rw

0

rw

0

rw

0

rw

0

rw

0

rw

0

rw

0

rw

0

rw

0

rw

0

rw

0

rw

0

rw

0

rw

Power-On Reset and System Resets

Read (r), Write (w), or Special (s) access