Maxq610 user’s guide – Maxim Integrated MAXQ610 User Manual

Page 91

5-19

MAXQ610 User’s Guide

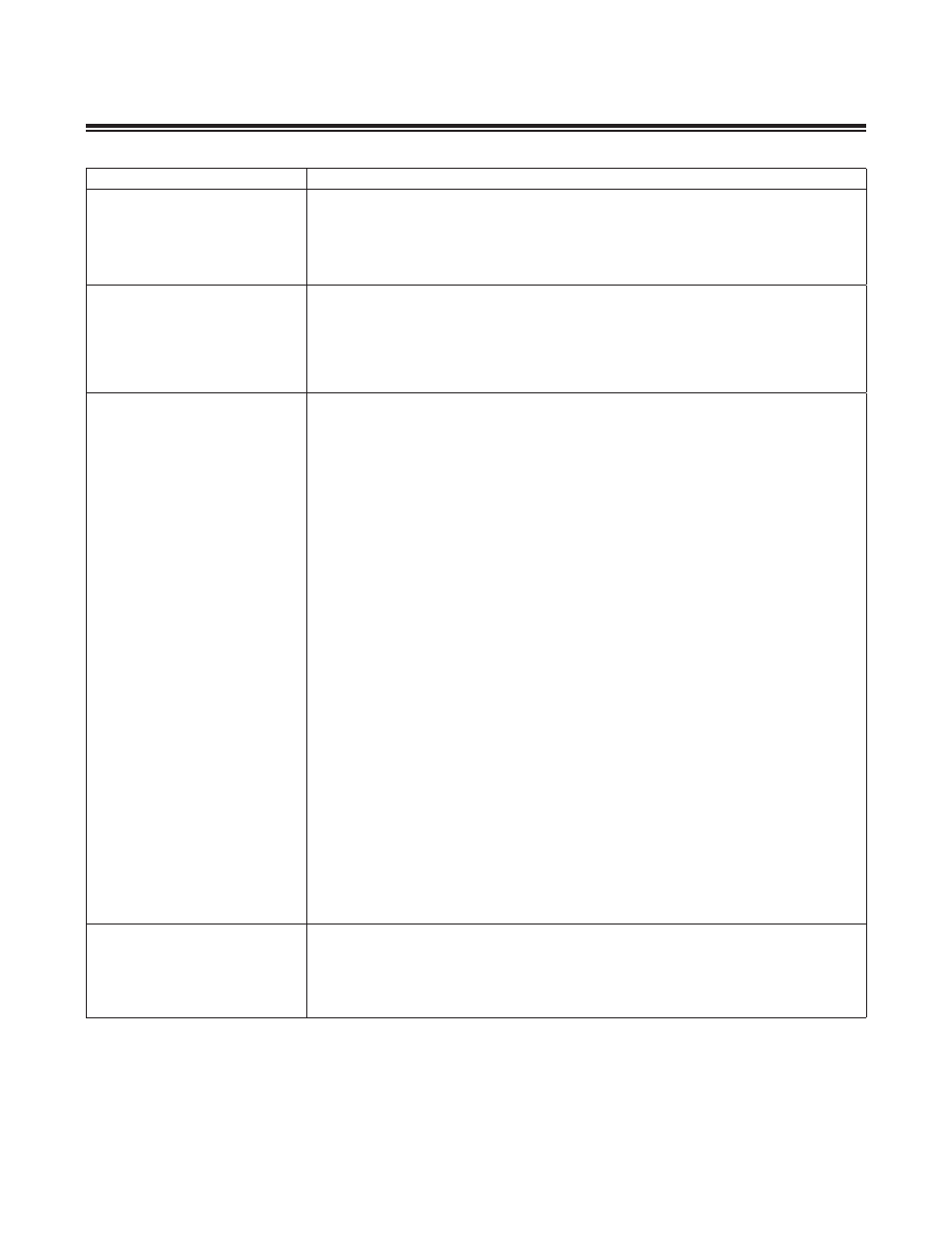

REGISTER

DESCRIPTION

SBUF1 (03h, 03h)

Serial Data Buffer 1

Initialization:

This buffer is cleared to 00h on all forms of reset .

Read/Write Access:

Unrestricted read/write .

SBUF1.7 to SBUF1.0

Serial Data Buffer 1 Bit 7:0. Data for serial port 0 is read from or written to this location .

The serial transmit and receive buffers are separate but both are addressed at this location .

SPIB (04h, 03h)

SPI Data Buffer (16-bit register)

Initialization:

This buffer is cleared to 0000h on all forms of reset .

Read/Write Access:

Unrestricted read, write is allowed outside of a transfer cycle; when the STBY bit is set, write

is blocked and causes write collision error .

SPIB.15 to SPIB.0

SPI Data Buffer Bits 15:0. Data for SPI is read from or written to this location . The serial

transmit and receive buffers are separate but both are addressed at this location .

SPICN (05h, 03h)

SPI Control Register

Initialization:

This buffer is cleared to 00h on all forms of reset .

Read/Write Access:

Unrestricted read/write except bit 7 is read-only .

SPICN.0 (SPIEN)

SPI Enable. Setting this bit to 1 enables the SPI module and its baud-rate generator for SPI

operation . Clearing this bit to 0 disables the SPI module and its baud-rate generator .

SPICN.1 (MSTM)

Master Mode Enable. MSTM functions as a master mode enable bit for the SPI module .

When MSTM is set to 1, the SPI operates as a master . When MSTM is cleared to 0, the

SPI module operates in slave mode . Note that this bit can be set from 0 to 1 only when the

SSEL signal is deasserted .

SPICN.2 (MODFE)

Mode Fault Enable. When set to 1 in master mode, this bit enables the use of SSEL input

as a mode fault signal; when cleared to 0, the SSEL has no function and its port pin can be

used for other purposes . In slave mode, the SSEL pin always functions as a slave select

input signal to the SPI module, independent of the setting of the MODFE bit .

SPICN.3 (MODF)

Mode Fault Flag. This bit is the mode fault flag when the SPI is operating as a master .

When mode fault detection is enabled as MODFE = 1 in master mode, a detection of a high

to low transition on the SSEL pin signifies a mode fault and sets the MODF to 1 . This bit

must be cleared to 0 by software once set . Setting this bit to 1 by software causes an inter-

rupt if enabled . This flag has no meaning in slave mode .

SPICN.4 (WCOL)

Write Collision Flag. This bit indicates a write collision when set to 1 . This is caused by

attempting to write to the SPIB while a transfer cycle is in progress . This bit must be cleared

to 0 by software once set . Setting this bit to 1 by software causes an interrupt if enabled .

SPICN.5 (ROVR)

Receive Overrun Flag. This bit indicates a receive overrun when set to 1 . This is caused

by two or more characters have been received since the last read by the processor . The

newer data is lost . This bit must be cleared to 0 by software once set . Setting this bit to 1 by

software causes an interrupt if enabled .

SPICN.6 (SPIC)

SPI Transfer Complete Flag. This bit indicates the completion of a transfer cycle when

set to 1 . This bit must be cleared to 0 by software once set . Setting this bit to 1 by software

causes an interrupt if enabled .

SPICN.7 (STBY)

SPI Transfer Busy Flag. This bit is used to indicate the current status of the SPI module .

STBY is set to 1 when starting a SPI transfer cycle and is cleared to 0 when the transfer

cycle is completed . This bit is controlled by hardware and is read-only for user software .

PR0 (08h, 03h)

Phase Register 0

Initialization:

The phase register is cleared to 0000h on all forms of reset .

Read/Write Access:

Unrestricted read/write .

PR0.15 to PR0.0

Phase Register Bits 15:0. This register is used to load and read the 16-bit value in the

phase register that determines the baud rate for the serial port 0 .