Maxq610 user’s guide – Maxim Integrated MAXQ610 User Manual

Page 90

5-18

MAXQ610 User’s Guide

REGISTER

DESCRIPTION

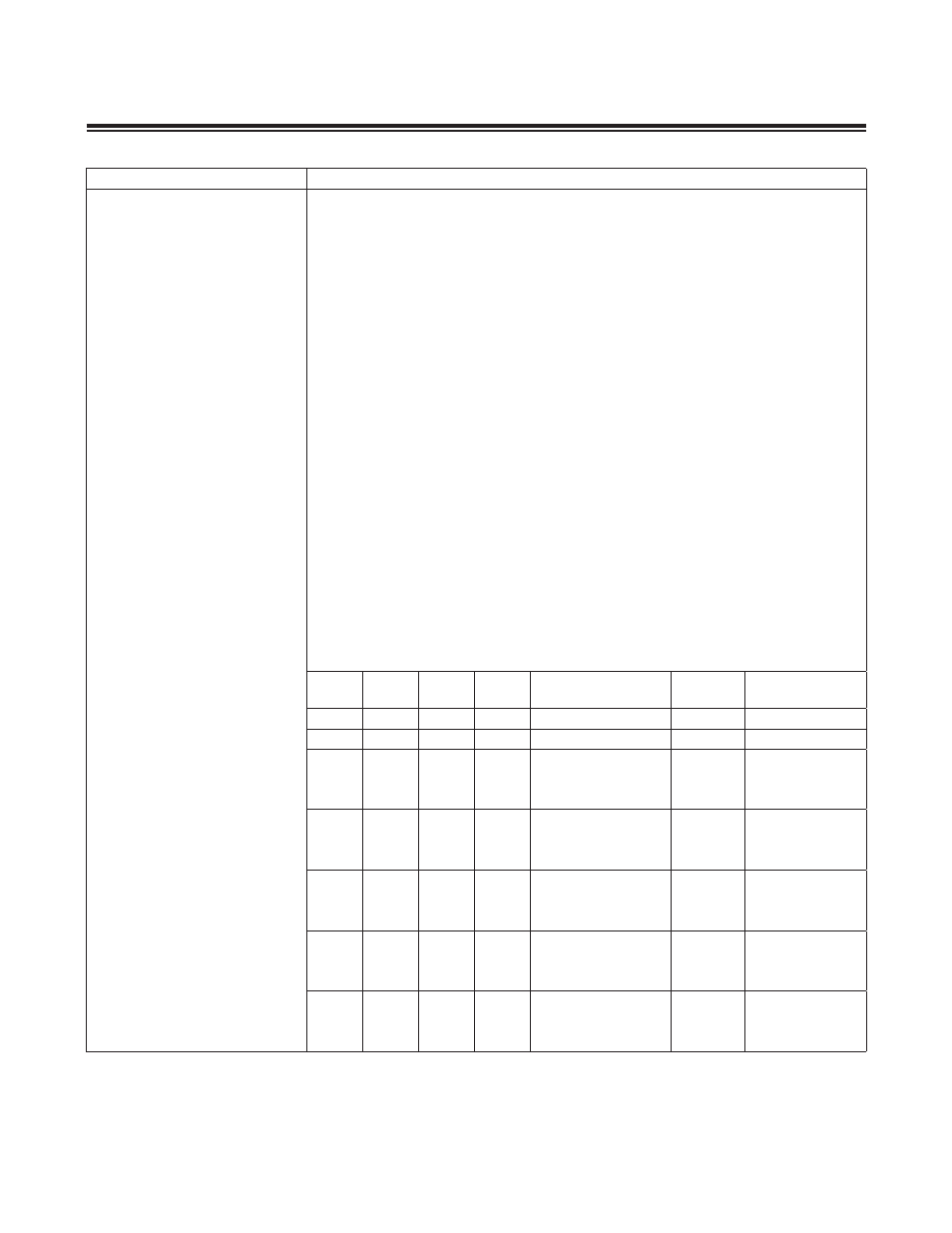

SCON1 (02h, 03h)

Serial Port 1 Control Register

Initialization:

The serial port control is cleared to 00h on all forms of reset .

Read/Write Access:

Unrestricted read/write .

SCON1.0 (RI)

Receive Interrupt Flag. This bit indicates that a data byte has been received in the serial

port buffer . The bit is set at the end of the 8th bit for mode 0, after the last sample of the

incoming stop bit for mode 1 subject to the value of the SM2 bit, or after the last sample of

RB8 for modes 2 and 3 . This bit must be cleared by software once set .

SCON1.1 (TI)

Transmit Interrupt Flag. This bit indicates that the data in the serial port data buffer has

been completely shifted out . It is set at the end of the last data bit for all modes of operation

and must be cleared by software once set .

SCON1.2 (RB8)

9th Received Bit State. This bit identifies the state of the 9th bit of received data in serial

port modes 2 and 3 . When SM2 is 0, it is the state of the stop bit in mode 1 . This bit has no

meaning in mode 0 .

SCON1.3 (TB8)

9th Transmission Bit State . This bit defines the state of the 9th transmission bit in serial

port modes 2 and 3 .

SCON1.4 (REN)

Receive Enable

REN_0 = 0: Serial port 0 receiver disabled .

REN_0 = 1: Serial port 0 receiver enabled for modes 1, 2, and 3 . Initiate synchronous

reception for mode 0 .

SCON1.5 (SM2)

Serial Port 1 Mode Bit 2. Setting this bit in mode 1 ignores reception if an invalid stop bit is

detected . Setting this bit in mode 2 or 3 enables multiprocessor communications, and pre-

vents the RI bit from being set and the interrupt from being asserted if the 9th bit received

is 0 . This bit also used to support mode 0 for clock selection:

SM2 = 0: Clock is divided by 12 .

SM2 = 1: Clock is divided by 4 .

SCON1.6 (SM1)

SCON1.7 (SM0/FE)

Serial Port 1 Mode Bits 1:0 (when FEDE is 0) . When FEDE is set to 1, this bit is the Framing

Error Flag that is set upon detection of an invalid stop bit . It must be cleared by software .

Modification of this bit when FEDE is set has no effect on the serial mode .

MODE

SM2

SM1

SM0

FUNCTION

LENGTH

(BITS)

PERIOD

0

0

0

0

Synchronous

8

12 system clocks

0

1

0

0

Synchronous

8

4 system clocks

1

x

1

0

Asynchronous

10

64/16 baud clocks

(SMOD = 0/1)

2

0

0

1

Asynchronous

11

64/32 system

clocks (SMOD =

0/1)

2

1

0

1

Asynchronous (MP)

11

64/32 system

clocks (SMOD =

0/1)

3

0

1

1

Asynchronous

11

64/16 baud clocks

(SMOD = 0/1)

3

1

1

1

Asynchronous (MP)

11

64/16 baud clocks

(SMOD = 0/1)