1 tap controller, 2 tap state control, 1 test-logic-reset – Maxim Integrated MAXQ610 User Manual

Page 146: 11 .1 tap controller -2 11 .2 tap state control -2, 11 .2 .1 test-logic-reset -2, Table 11-1 . tap signals -2, Maxq610 user’s guide

11-2

MAXQ610 User’s Guide

SECTION 11: TEST ACCESS PORT (TAP)

The MAXQ610 microcontroller incorporates a test access port (TAP) and TAP controller for communication with a host

device across a 4-wire synchronous serial interface . The TAP can be used by MAXQ610 microcontrollers to support in-

system programming and/or in-circuit debug . The TAP is compatible with the JTAG IEEE standard 1149 and is formed

by four interface signals as described in Table 11-1 . For detailed information on the TAP and TAP controller, refer to

IEEE Std 1149 .1 “IEEE Standard Test Access Port and Boundary-Scan Architecture .”

11.1 TAP Controller

The TAP controller is a synchronous state machine that responds to changes at the TMS and TCK signals . Based on

its state transition, the controller provides the clock and control sequence for TAP operation .

The performance of the TAP is dependent on the TCK clock frequency . The maximum TCK clock frequency should be

limited to 1/8th the system clock frequency . This section provides a brief description of the state machine and its state

transitions . The state diagram in Figure 11-1 summarizes the transitions caused by the TMS signal sampling on the

rising edge at TCK . The TMS signal value is presented adjacent to each state transition in the figure .

11.2 TAP State Control

The TAP provides an independent serial channel to communicate synchronously with the host system . The TAP state

control is achieved through host manipulation of the test-mode select (TMS) and test clock (TCK) signals . The TMS

signal is sampled at the rising edge of TCK and decoded by the TAP controller to control movement between the TAP

states . The TDI input and TDO output are meaningful once the TAP is in a serial shift state (i .e ., shift-IR or shift-DR) .

11.2.1 Test-Logic-Reset

On a power-on reset, the TAP controller is initialized to the test-logic-reset state and the instruction register (IR[2:0]) is

initialized to the bypass instruction so that it does not affect normal system operation . No matter what the state of the

controller, it enters test-logic-reset when TMS is held high for at least five rising edges of TCK . The controller remains

in the test-logic-reset state if TMS remains high . An erroneous low signal on the TMS may cause the controller to move

into the run-test-idle state, but no disturbance is caused to system operation if the TMS signal is returned and kept at

the intended logic high for three rising edges of TCK since this returns the controller to the test-logic-reset state .

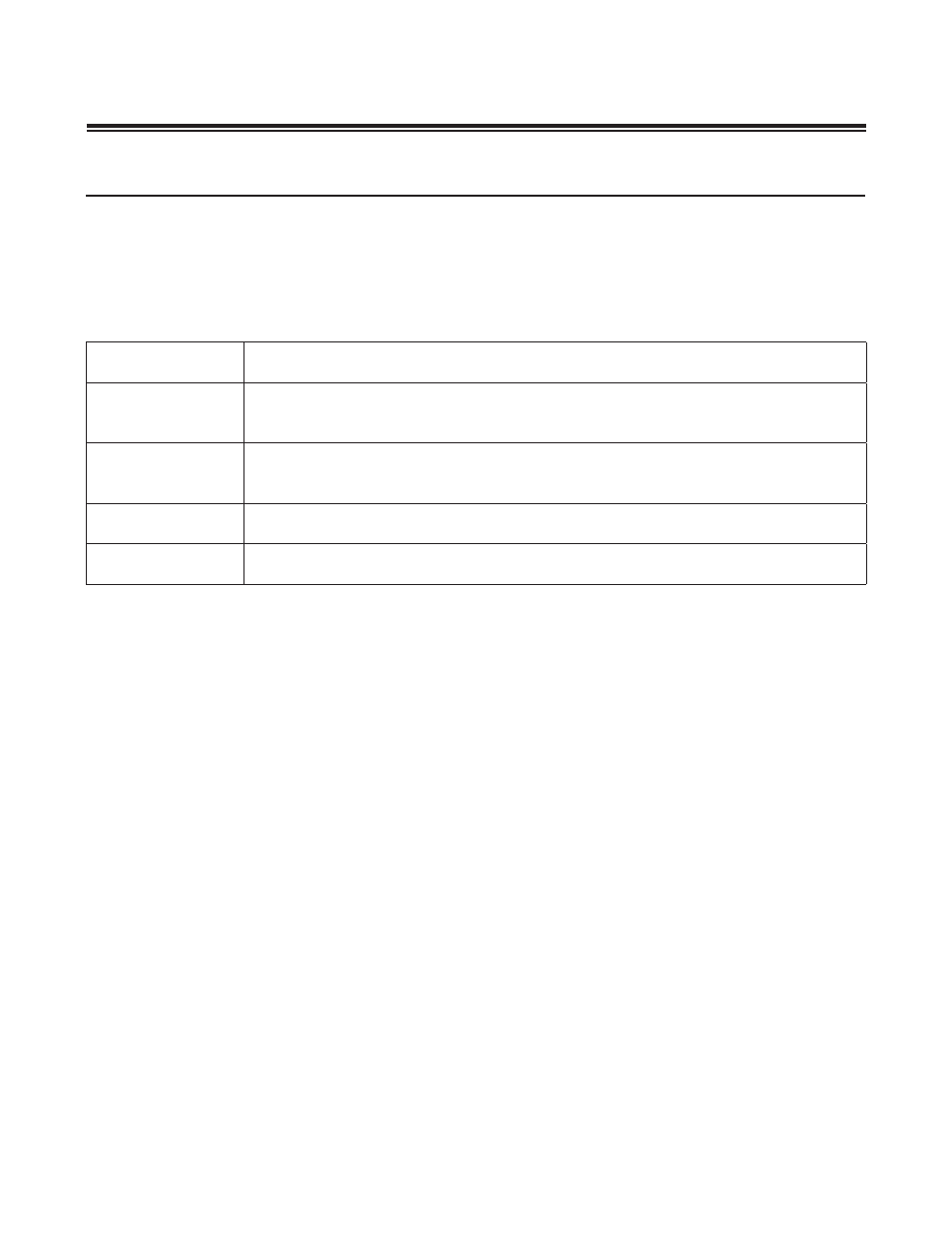

Table 11-1. TAP Signals

EXTERNAL PIN

SIGNAL

DESCRIPTION

TDO: Test Data Output

Serial Data Output Pin . This signal is used to serially transfer internal data to the external host . Data

is transferred least significant bit first . Data is driven out only on the falling edge of TCK, only during

TAP shift-IR or shift-DR states and is otherwise inactive .

TDI: Test Data Input

Serial Data Input Pin . This signal is used to receive data serially transferred by the host . Data is

received least significant bit first and is sampled on the rising edge of TCK . TDI is weakly pulled high

internally when TAP = 1 .

TCK: Test Clock Input

Serial Shift Clock Provided by the Host . When this signal is stopped at 0, storage elements in the TAP

logic must retain their data indefinitely . TCK is weakly pulled high internally when TAP = 1 .

TMS: Test-Mode Select

Input

Mode Select Input Pin . This signal is sampled at the rising edge of TCK and controls movement

between TAP states . TMS is weakly pulled high internally when TAP = 1 .