Table 5-3 . peripheral register reset values -3, Maxq610 user’s guide – Maxim Integrated MAXQ610 User Manual

Page 75

5-3

MAXQ610 User’s Guide

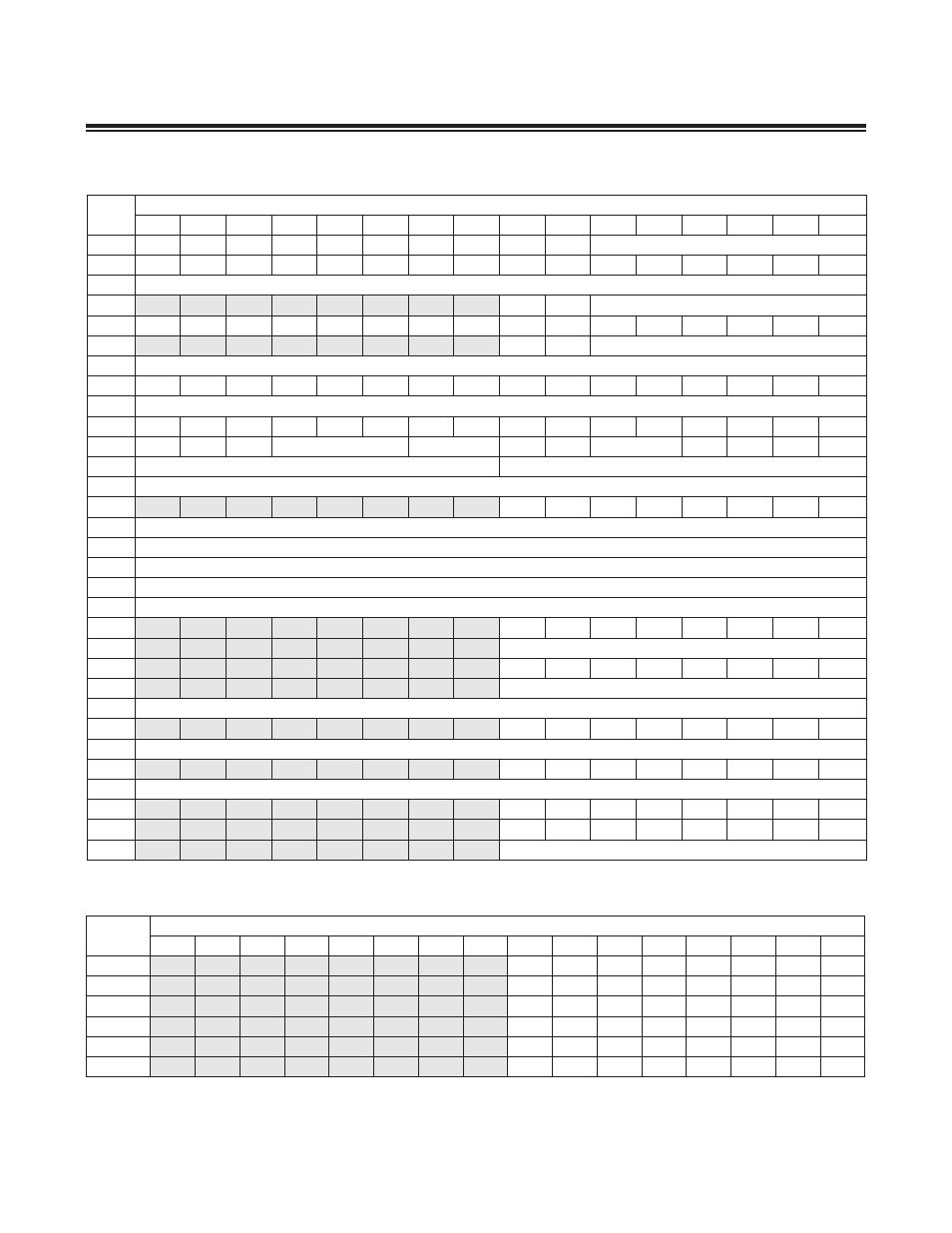

Table 5-3. Peripheral Register Reset Values

Table 5-2. Peripheral Register Bit Function (continued)

REG

BIT

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

PO4

—

—

PO4[5:0]

WUTC

—

—

—

—

—

—

WTF

WTE

WUT

WUT[15:0]

PI4

—

—

PI4[5:0]

PWCN

—

—

—

—

—

—

PFRCK1 PFRCK0 PFRST IRRXWP IRTXOUT IRTXOE REGEN

PFI

PFIE

PFD

PD4

—

—

PD4[5:0]

TB0R

TB0R[15:0]

TB0CN

C/TB

—

—

TBCS

TBCR

TBPS2 TBPS1 TBPS0

TFB

EXFB

TBOE

DCEN

EXENB

TRB

ETB

CP/RLB

TB1R

TB1R[15:0]

TB1CN

C/TB

—

—

TBCS

TBCR

TBPS2 TBPS1 TBPS0

TFB

EXFB

TBOE

DCEN

EXENB

TRB

ETB

CP/RLB

IRCN

—

—

—

IRDIV[2:0]

IRENV[1:0]

IRXRL

IRCFME

IRRXSEL[1:0]

IRDATA IRTXPOL IRMODE

IREN

IRCA

IRCAH[7:0]

IRCAL[7:0]

IRMT

IRMT[15:0]

IRCNB

—

—

—

—

RXBCNT

IRIE

IRIF

IROV

TB0C

TB0C[15:0]

TB0V

TB0V[15:0]

TB1C

TB1C[15:0]

TB1V

TB1V[15:0]

IRV

IRV[15:0]

SCON0

SM0/FE

SM1

SM2

REN

TB8

RB8

TI

RI

SBUF0

SBUF0[7:0]

SCON1

SM0/FE

SM1

SM2

REN

TB8

RB8

TI

RI

SBUF1

SBUF1[7:0]

SPIB

SPIB[15:0]

SPICN

STBY

SPIC

ROVR

WCOL

MODF

MODFE

MSTM

SPIEN

PR0

PR0[15:0]

SMD0

—

—

—

—

—

ESI0

SMOD0

FEDE0

PR1

PR1[15:0]

SMD1

—

—

—

—

—

ESI1

SMOD1

FEDE1

SPICF

ESPII

SAS

—

—

—

CHR

CKPHA CKPOL

SPICK

CKR[7:0]

REG

BIT

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

PO0

0

0

0

0

0

0

0

0

PO1

0

0

0

0

0

0

0

0

PO2

0

0

0

0

0

0

0

0

PO3

0

0

0

0

0

0

0

0

EIF0

0

0

0

0

0

0

0

0

EIE0

0

0

0

0

0

0

0

0

- DS80C390 (58 pages)

- DS5001FP (26 pages)

- MAX1416 (14 pages)

- MAX5865 (18 pages)

- DS33Z41 (167 pages)

- MAX1202 (7 pages)

- USBTO232 (31 pages)

- HFAN-09.5.0: Pattern Creator/Converter Software (8 pages)

- MAX-IDE MAXQ Microcontrollers (11 pages)

- MAX6876 Power-Supply Tracker/Sequencer (6 pages)

- MAX6877 Power-Supply Tracker/Sequencer (3 pages)

- 78Q8430 ARM9(920T) Linux Driver Diagnostic Guide (19 pages)

- 78Q8430 Software Driver (54 pages)

- 78Q8430 ST 5100/OS-20 with NexGen TCP/IP Stack (28 pages)

- 6612_OMU_S2_URT_V1_13 (56 pages)

- 6612_OMU_S2+2_URT_V1_14 (58 pages)

- 71M6511 Power Meter IC Family Software (137 pages)

- 71M65xx ADM51 ICE Safety Notice (2 pages)

- 71M6511 2-Layer Demo Board (2 pages)

- 71M6511 4-Layer Demo Board (2 pages)

- 78Q8430 Linux Driver ARM Platform (22 pages)

- 71M6513 Demo Board (2 pages)

- 71M6521DE Energy Meter IC Family Software (138 pages)

- 71M6521 Demo Board (2 pages)

- 71M6531 Demo Board (2 pages)

- 71M6531 Energy Meter IC Family Software (116 pages)

- 71M6533 Demo Board (2 pages)

- 71M6534H Demo Board (2 pages)

- 71M6515H Demo Board (2 pages)

- 73S1209F Evaluation Board (2 pages)

- 73S12xxF (38 pages)

- 73S12xxF Software (93 pages)

- 73S1210F Evaluation Board Lite (2 pages)

- 73S1210F Evaluation Board (2 pages)

- 73S1210F Multi-SAM Evaluation Board Lite (2 pages)

- 73S12xxF USB-CCID Linux DFU Host Application (8 pages)

- 73S1215F Device Firmware Upgrade Host Driver/Application (10 pages)

- 73S12xxF USB-CCID Host GUI (22 pages)

- 73S1215F Windows XP 32 USB CCID and DFU Drivers (15 pages)

- 73S1215F CCID USB Linux Driver (16 pages)

- 73S1215F Evaluation Board (2 pages)

- 73S1215F Evaluation Board Lite (2 pages)

- 73S1217F Evaluation Board (2 pages)

- 73S1217F Evaluation Board Lite (2 pages)

- MAXQ Family (216 pages)