Maxq610 user’s guide – Maxim Integrated MAXQ610 User Manual

Page 63

4-8

MAXQ610 User’s Guide

REGISTER

DESCRIPTION

IC, 8h[5h]

Interrupt and Control Register (8

bits)

Initialization

This register is cleared to 0Ch on all forms of reset .

Access

Unrestricted direct read . Write access to bits 0, 4, 5, 6, 7 only . See bit descriptions for

details .

IC.0 (IGE)

Interrupt Global Enable

If this bit is set to 1, interrupts can be enabled individually .

If this bit is set to 0, all interrupts are disabled (except the power-fail warning interrupt,

which is enabled solely by its interrupt enable (PFIE)) .

IC.1

Reserved . Reads return 0 .

IC.2 (IPS0)

Interrupt Priority Status 0

IC.3 (IPS1)

Interrupt Priority Status 1. These read-only bits are set to 11b if the processor is not

serving an interrupt . These bits are updated by the interrupt handler in response to an

interrupt request . Any value other than 11b indicates that the processor is currently execut-

ing an interrupt service routine with the specified priority . These bits are set to 11b when

the processor executes the corresponding RETI instruction .

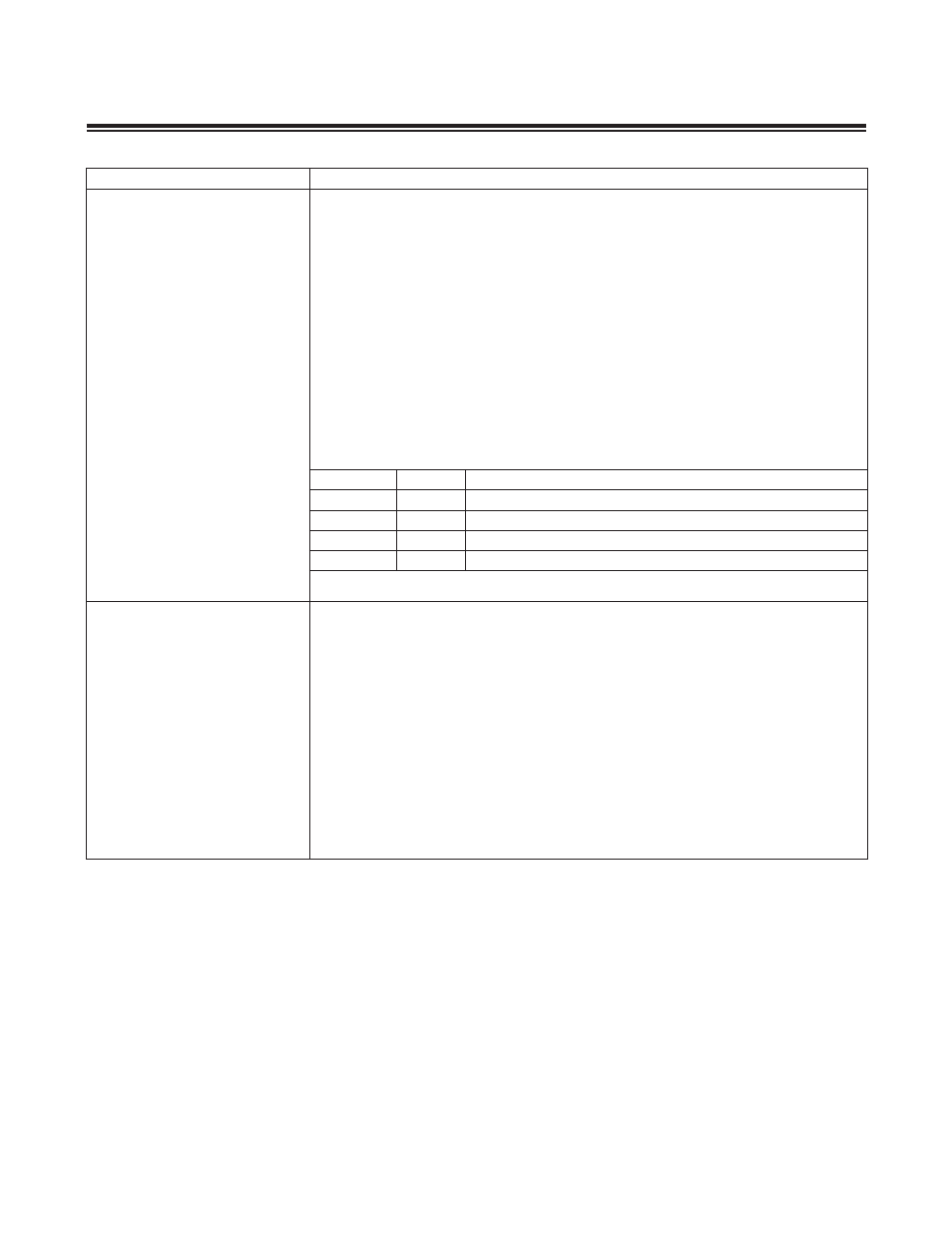

IPS1

IPS0

FUNCTION

0

0

Serving a level 0 (highest priority) interrupt

0

1

Serving a level 1 interrupt

1

0

Serving a level 2 (lowest priority) interrupt

1

1

Not serving any interrupt

IC.7 to IC.4

Reserved . Reads return 0 .

PRIVT1, 08h[06h]

Privilege Register Atomic 1 (8 bits)

Initialization

This register is reset to 00h on all resets .

Bits 3 and 2 are cleared by hardware when the current IP is not in utility ROM code, nor

system code .

Bits 1 and 0 are cleared by hardware when the current IP is not in utility ROM, system, nor

user loader code .

Access

Bits 3 and 2 can only be written by utility ROM code, or system code . Bits 1 and 0 can

only be written by utility ROM code, system code, or user loader code . No read access .

PRIVT1.3 to PRIVT1.0

Privilege Atomic 1 Bits. These bits default to 0 on a power-on reset . The bits are used as

a logical AND bit mask . Writing these bits sets the corresponding bits in the PRIV register

using the PRIVT0 register as a logical AND bit mask:

PRIV = (PRIVT0) AND (PRIVT1) .

Writing to PRIVT1 clears the PRIVT0 register .

PRIVT1.7 to PRIVT1.4

Reserved . Reads return 0 .